STA1095 Description

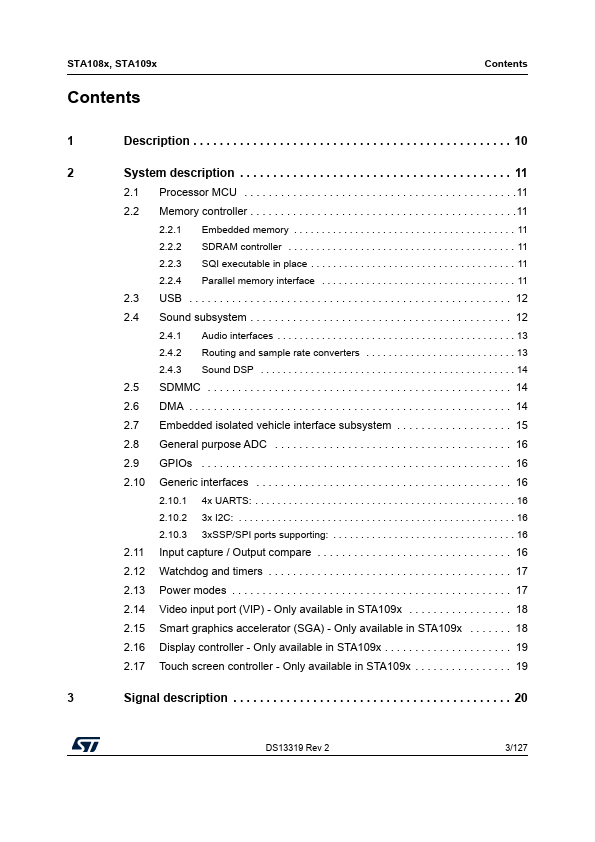

10 2 System description . .11 2.2 Memory controller . .11 2.2.1 Embedded memory.

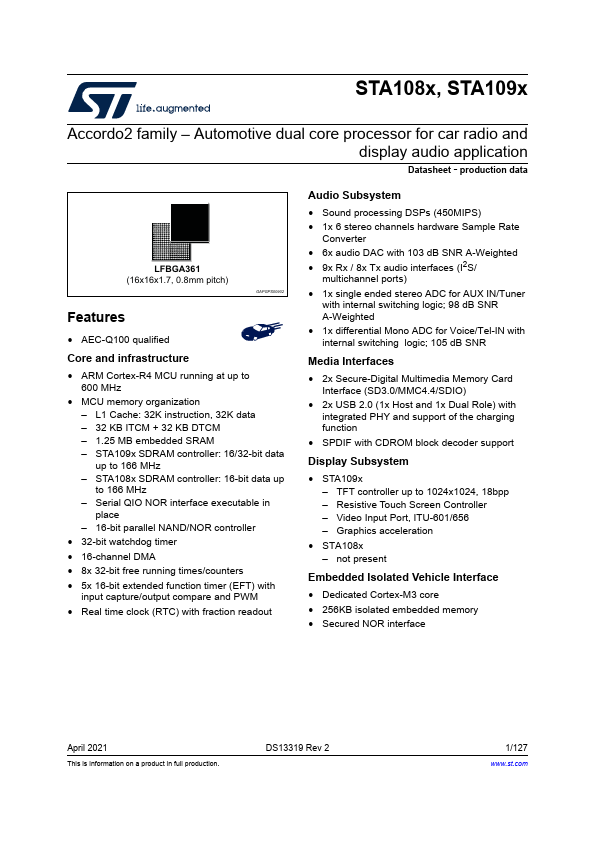

STA1095 Key Features

- AEC-Q100 qualified

- ARM Cortex-R4 MCU running at up to 600 MHz

- MCU memory organization

- L1 Cache: 32K instruction, 32K data

- 32 KB ITCM + 32 KB DTCM

- 1.25 MB embedded SRAM

- STA109x SDRAM controller: 16/32-bit data up to 166 MHz

- STA108x SDRAM controller: 16-bit data up to 166 MHz

- Serial QIO NOR interface executable in place

- 16-bit parallel NAND/NOR controller