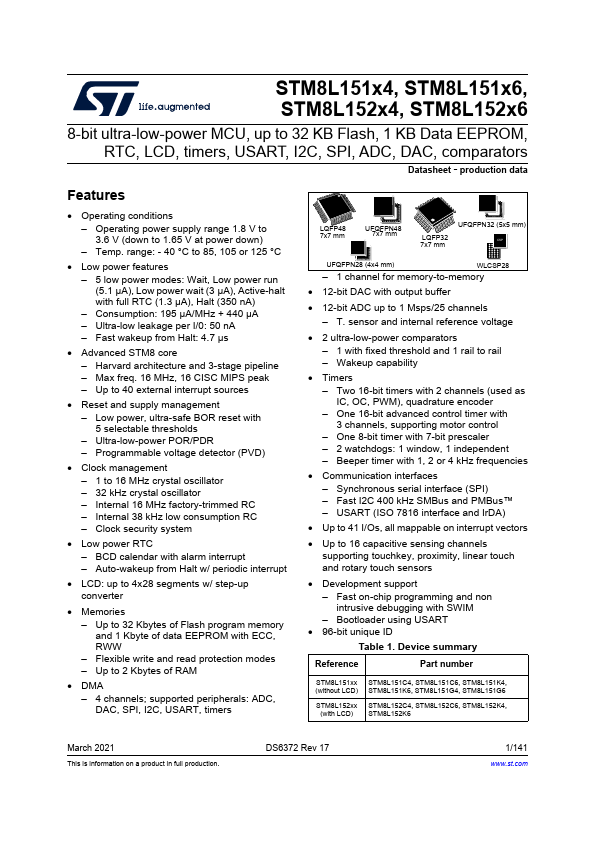

STM8L151C4

Key Features

- Advanced STM8 core - Harvard architecture and 3-stage pipeline - Max freq. 16 MHz, 16 CISC MIPS peak - Up to 40 external interrupt sources

- Low power RTC - BCD calendar with alarm interrupt - Auto-wakeup from Halt w/ periodic interrupt

- LCD: up to 4x28 segments w/ step-up converter

- 1 channel for memory-to-memory

- 12-bit DAC with output buffer

- 12-bit ADC up to 1 Msps/25 channels - T. sensor and internal reference voltage

- 2 ultra-low-power parators

- 1 with fixed threshold and 1 rail to rail - Wakeup capability

- Two 16-bit timers with 2 channels (used as IC, OC, PWM), quadrature encoder

- One 16-bit advanced control timer with 3 channels, supporting motor control