STR910FAW32

STR910FAW32 is 16/32-Bit Flash MCU manufactured by STMicroelectronics.

- Part of the STR910FAM32 comparator family.

- Part of the STR910FAM32 comparator family.

..

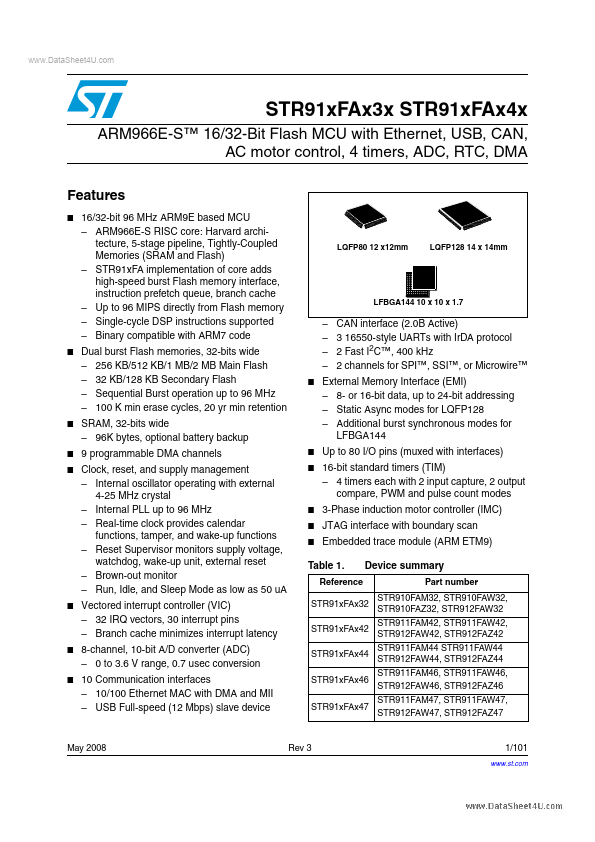

STR91x FAx3x STR91x FAx4x

ARM966E-S™ 16/32-Bit Flash MCU with Ethernet, USB, CAN, AC motor control, 4 timers, ADC, RTC, DMA

Features

- 16/32-bit 96 MHz ARM9E based MCU

- ARM966E-S RISC core: Harvard architecture, 5-stage pipeline, Tightly-Coupled Memories (SRAM and Flash)

- STR91x FA implementation of core adds high-speed burst Flash memory interface, instruction prefetch queue, branch cache

- Up to 96 MIPS directly from Flash memory

- Single-cycle DSP instructions supported

- Binary patible with ARM7 code Dual burst Flash memories, 32-bits wide

- 256 KB/512 KB/1 MB/2 MB Main Flash

- 32 KB/128 KB Secondary Flash

- Sequential Burst operation up to 96 MHz

- 100 K min erase cycles, 20 yr min retention SRAM, 32-bits wide

- 96K bytes, optional battery backup 9 programmable DMA channels Clock, reset, and supply management

- Internal oscillator operating with external 4-25 MHz crystal

- Internal PLL up to 96 MHz

- Real-time clock provides calendar functions, tamper, and wake-up functions

- Reset Supervisor monitors supply voltage, watchdog, wake-up unit, external reset

- Brown-out monitor

- Run, Idle, and Sleep Mode as low as 50 u A Vectored interrupt controller (VIC)

- 32 IRQ vectors, 30 interrupt pins

- Branch cache minimizes interrupt latency 8-channel, 10-bit A/D converter (ADC)

- 0 to 3.6 V range, 0.7 usec conversion 10 munication interfaces

- 10/100 Ethernet MAC with DMA and MII

- USB Full-speed (12 Mbps) slave device

- -

LQFP80 12 x12mm

LQFP128 14 x 14mm

LFBGA144 10 x 10 x...