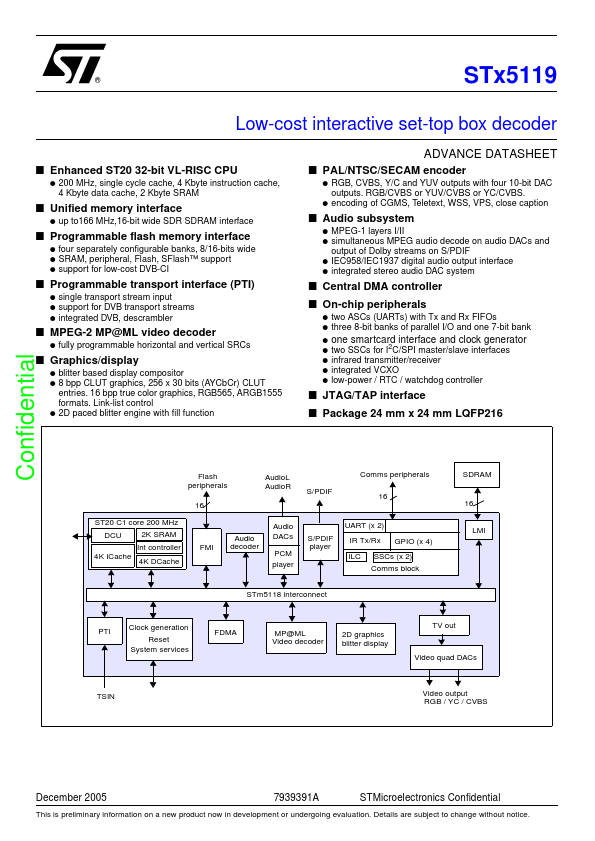

STi5119

STi5119 is Low-cost interactive set-top box decoder manufactured by STMicroelectronics.

Confidential

® STx5119

Low-cost interactive set-top box decoder

I Enhanced ST20 32-bit VL-RISC CPU

G 200 MHz, single cycle cache, 4 Kbyte instruction cache, 4 Kbyte data cache, 2 Kbyte SRAM

I Unified memory interface

G up to166 MHz,16-bit wide SDR SDRAM interface

I Programmable flash memory interface

G four separately configurable banks, 8/16-bits wide G SRAM, peripheral, Flash, SFlash™ support G support for low-cost DVB-CI

I Programmable transport interface (PTI)

G single transport stream input G support for DVB transport streams G integrated DVB, descrambler

I MPEG-2 MP@ML video decoder

G fully programmable horizontal and vertical SRCs

I Graphics/display

G blitter based display...