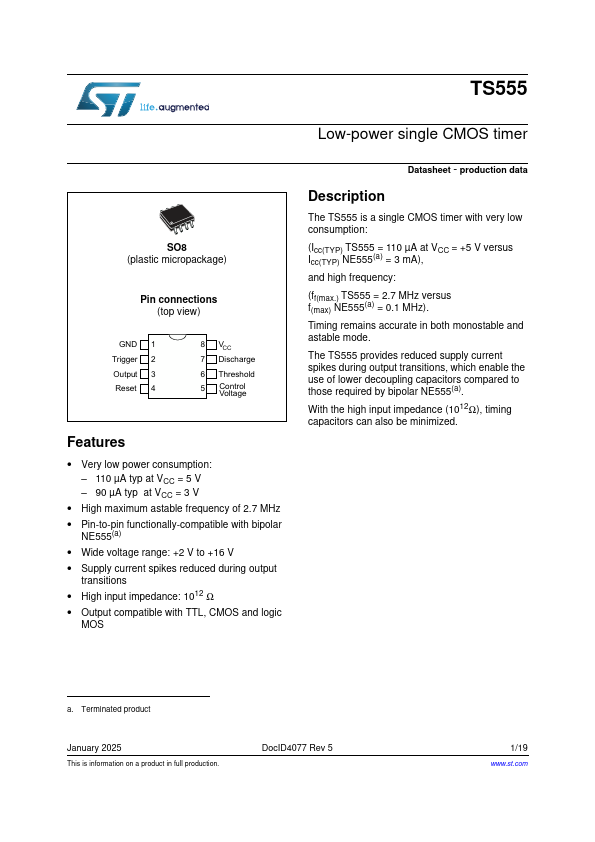

TS555

Features

- Very low power consumption:

- 110 µA typ at VCC = 5 V

- 90 µA typ at VCC = 3 V

- High maximum astable frequency of 2.7 MHz

- Pin-to-pin functionally-patible with bipolar

NE555(a)

- Wide voltage range: +2 V to +16 V

- Supply current spikes reduced during output transitions

- High input impedance: 1012 Ω

- Output patible with TTL, CMOS and logic

- production data

Description

The TS555 is a single CMOS timer with very low consumption:

(Icc(TYP) TS555 = 110 µA at VCC = +5 V versus Icc(TYP) NE555(a) = 3 m A), and high frequency:

(ff(max.) TS555 = 2.7 MHz versus f(max) NE555(a) = 0.1 MHz). Timing remains accurate in both monostable and astable mode.

The TS555 provides reduced supply current spikes during output transitions, which enable the use of lower decoupling capacitors pared to those required by bipolar NE555(a). With the high input impedance (1012Ω), timing capacitors can also be minimized. a. Terminated product

January 2025

This is information on a product...

Representative TS555 image (package may vary by manufacturer)