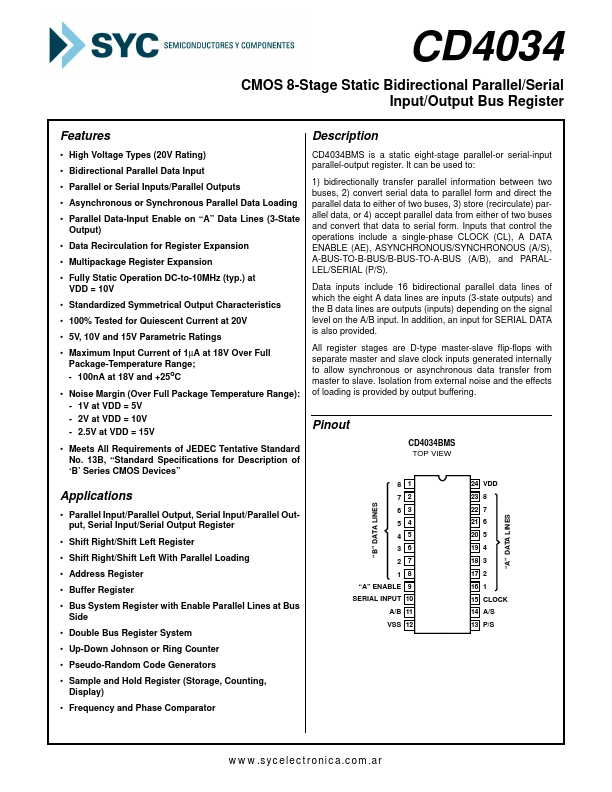

Description

High Voltage Types (20V Rating) Bidirectional Parallel Data Input Parallel or Serial Inputs/Parallel Outputs Asynchronous or Synchronous Parallel Data Loading Parallel Data-Input Enable on “A” Data Lines (3-State Output) Data Recirculation for Register Expansion Multipackage Register Expansion Fully Static Operation DC-to-10MHz (typ.) at VDD = 10V Standardized Symmetrical Output Characteristics 100% Tested for Quiescent Current at 20V 5V, 10V and 15V Parametric Ratings Maximum Input Current of 1µA at 18V Over Full Package-Temperature Range; - 100nA at 18V and +25oC Noise Margin (Over Full Package Temperature Range): - 1V at VDD = 5V - 2V at VDD = 10V - 2.5V at VDD = 15V Meets All Requirements of JEDEC Tentative Standard No. 13B, “Standard Specifications for Description of ‘B’ Series CMOS Devices”.