Datasheet Summary

S T M4472

S amHop Microelectronics C orp. Jan.7 ,2008 ver1.0

N- Channel Enhancement Mode Field Effect Transistor

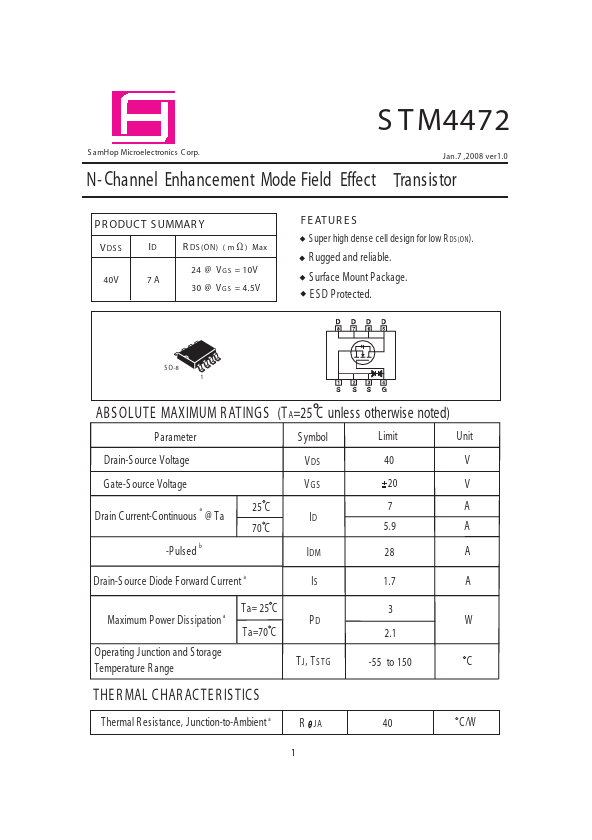

P R ODUC T S UMMAR Y

V DS S

40V

F E AT UR E S S uper high dense cell design for low R DS (ON ).

7A

R DS (ON) ( m ıΩ ) Max

24 @ V G S = 10V 30 @ V G S = 4.5V

R ugged and reliable. S urface Mount P ackage. E S D P rotected.

S O-8 1

ABS OLUTE MAXIMUM R ATINGS (T A=25 C unless otherwise noted)

P arameter Drain-S ource Voltage Gate-S ource Voltage Drain C urrent-C ontinuous @ Ta -P ulsed b a

S ymbol V DS V GS 25 C 70 C IDM IS PD Ta=70 C T J , T S TG ID

Limit 40 20 7 5.9 28 1.7 3 2.1 -55 to 150

Unit V V A A A A W C

Drain-S ource Diode Forward C urrent a Maximum P ower...