Datasheet Summary

Preliminary CMOS SDRAM

512Mbit SDRAM

32M x 4bit x 4 Banks Synchronous DRAM LVTTL

..

Revision 0.2 Dec. 2001

Samsung Electronics reserves the right to change products or specification without notice.

Rev. 0.2 Dec. 2001

Revision History

Revision 0.0 (Mar. 2001) Revision 0.1 (Aug. 2001)

Defined target DC characteristics.

Preliminary CMOS SDRAM

Revision 0.2 (Dec. 2001)

- - Changed "Target" to "Preliminary". Redefined DC characteristics.

Rev. 0.2 Dec. 2001

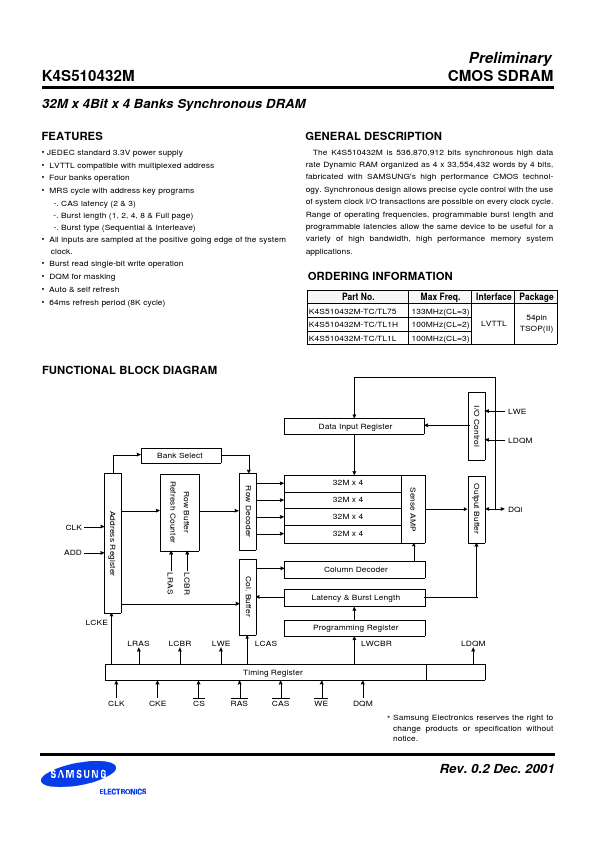

32M x 4Bit x 4 Banks Synchronous DRAM

Features

- JEDEC standard 3.3V power supply

- LVTTL patible with multiplexed address

- Four banks operation

- MRS cycle with address key...