Datasheet Summary

S3C8075/P8075

PRODUCT OVERVIEW

PRODUCT OVERVIEW

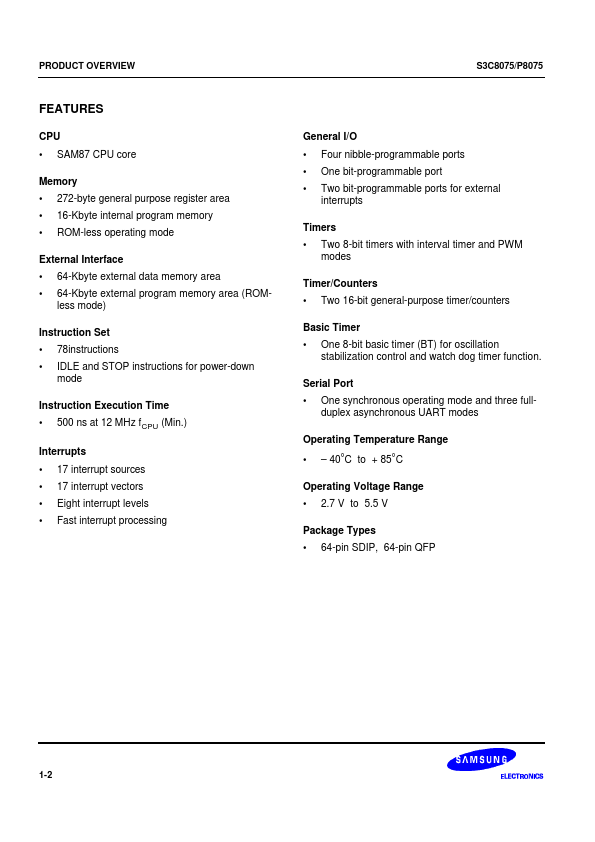

SAM8 PRODUCT FAMILY

Samsung's SAM87 family of 8-bit single-chip CMOS microcontrollers offers a fast and efficient CPU, a wide range of integrated peripherals, and various mask-programmable ROM sizes. Important CPU Features include:

- Efficient register-oriented architecture

- Selectable CPU clock sources

- Idle and Stop power-down mode release by interrupt

- Built-in basic timer with watchdog function A sophisticated interrupt structure recognizes up to eight interrupt levels. Each level can have one or more interrupt sources and vectors. Fast interrupt processing (within a minimum of six CPU clocks) can be assigned to specific...