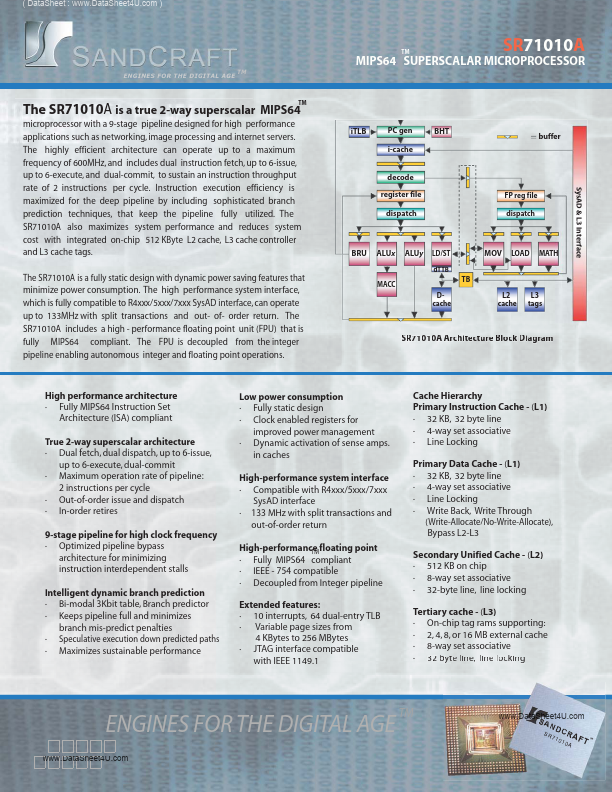

SR71010A Overview

Key Features

- Fully MIPS64 Instruction Set Architecture (ISA) compliant True 2-way superscalar architecture

- Dual fetch, dual dispatch, up to 6-issue, up to 6-execute, dual-commit

- Maximum operation rate of pipeline: 2 instructions per cycle

- Out-of-order issue and dispatch

- In-order retires 9-stage pipeline for high clock frequency