Datasheet Summary

..

H S 3120

D ouble Buffered 12-Bit MD AC

FEA TURES

- M onolithic Construction

- 12 Bit Resolution

- 0.01% Non-Linearity

- jup patible

- 4-Quadrant M ultiplication

- Latch-up Protected

Sipex D ata Converter Line

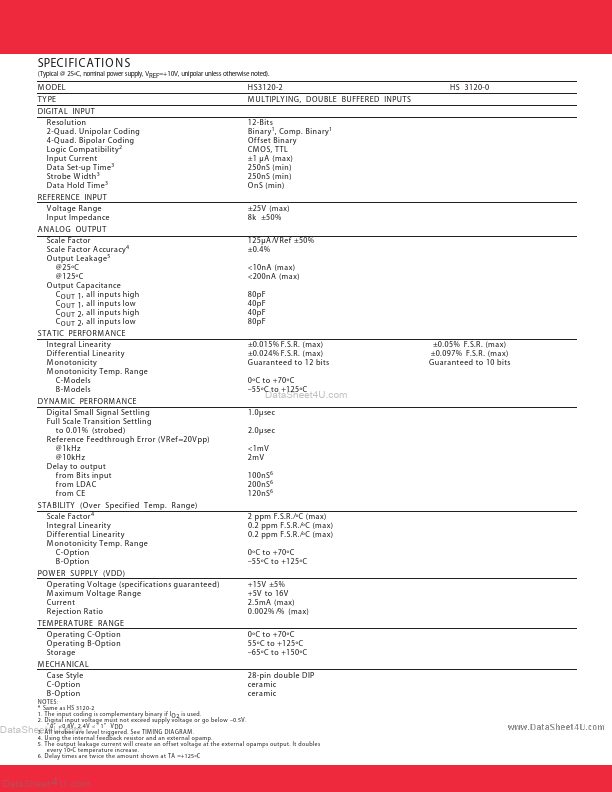

DESCRIPTION The HS 3120 is a precision monolithic 12-bit multiplying DA C with internal two-stage input storage registers for easy interfacing with microprocessor busses. It is packaged in a 28-pin DIP to give high I/O design flexibility. DOUBLE BUFFERED

- The input registers are sectioned controls are level-triggered to allow static or dynamic into 3 segments of 4 bits each, all individually operation. addressable. The DA C-register, following the input V...