SED1351

SED1351 is Graphics LCD Controller manufactured by Seiko Instruments.

DESCRIPTION

The SED1351F is a graphics LCD controller capable of controlling medium to large resolution displays. It transfers data from MPU to external frame buffer RAM and converts this data to display signals for LCD drivers. The SED1351F can display images with 4 gray shades and support display duty cycle as high as 1/ 1024. The SED1351F is designed to achieve high efficiency and data throughput to the LCD. It has a cycle steal mode which allows MPU to access frame buffer RAM without interfering with the display operation. The SED1351F can directly interface with up to eight 64K-bit SRAMs or two 256K-bit SRAMs. The SED1351F can operate with either 5V or 3V power supply. The 5V version chip is the SED1351F0A and the 3V version chip is the SED1351FLB. s FEATURES

- Low-power CMOS technology

- 8-bit or 16-bit MPU data interface

- Direct interface with 80xx, Z80 and 68xxx MPU or 8-bit panel data bus for single panel and

- 44-bit bus for dual panel

- Support logical OR of layers and panel division

- Smooth vertical scrolling

- Virtual screen display up to 1024 mode (on/off only) generates black &

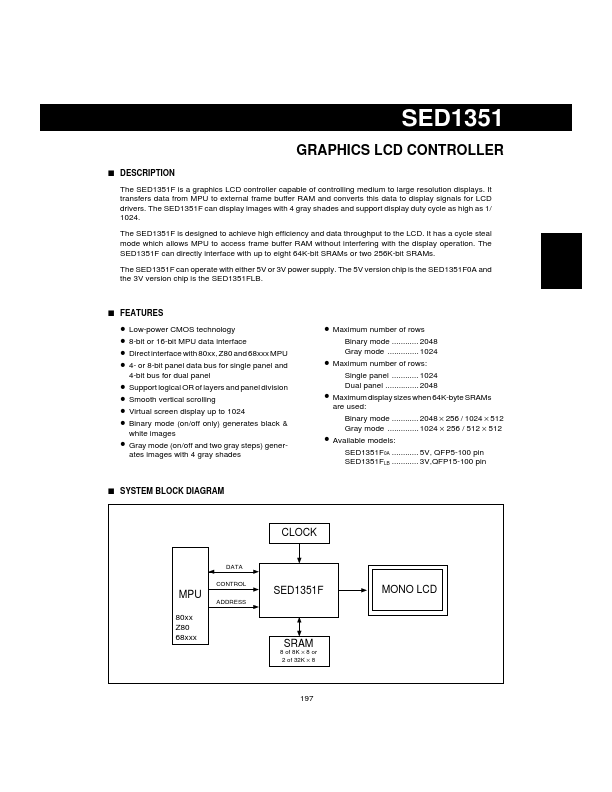

- Binary white images mode (on/off and two gray steps) gener- Gray ates images with 4 gray shades s SYSTEM BLOCK DIAGRAM

- Maximum number of rows

- -

- Binary mode 2048 Gray mode 1024 Maximum number of rows: Single panel 1024 Dual panel 2048 Maximum display sizes when 64K-byte SRAMs are used: Binary mode 2048 × 256 / 1024 × 512 Gray mode 1024 × 256 / 512 × 512 Available models: SED1351F0A 5V, QFP5-100 pin SED1351FLB 3V,QFP15-100 pin

CLOCK

DATA CONTROL

80xx Z80 68xxx

SED1351F

MONO LCD

ADDRESS

8 of 8K × 8 or 2 of 32K × 8

SRAM

SED1351 s INTERFACE WITH 8-BIT MPU (Z-80) AND 64K-BIT SRAM (8 of 8K x 8)

Z80

A0~A15 DECODER MMU DECODER MEMRQ IOREQ

SED1351F

A0~A15 IOCS MPUSEL

UD0~UD3,LD0~LD3 YD LP XSCL FR MONO LCD

MEMCS

VA0~VA12 VD0~VD7 VCS0~VCS7...