ACS1790T

Overview

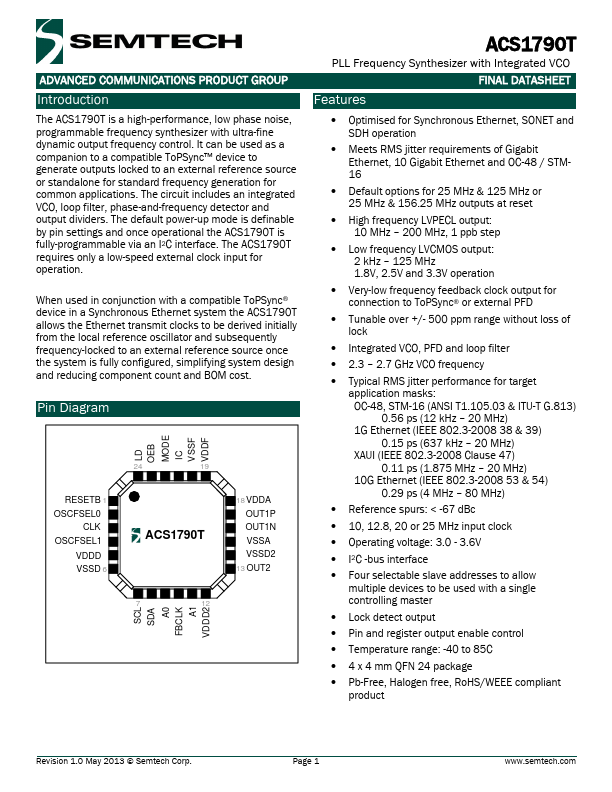

The ACS1790T is a high-performance, low phase noise, programmable frequency synthesizer with ultra-fine dynamic output frequency control. It can be used as a companion to a compatible ToPSync™ device to generate outputs locked to an external reference source or standalone for standard frequency generation for common applications.

- Optimised for Synchronous Ethernet, SONET and SDH operation

- Meets RMS jitter requirements of Gigabit Ethernet, 10 Gigabit Ethernet and OC-48 / STM16

- Default options for 25 MHz & 125 MHz or 25 MHz & 156.25 MHz outputs at reset

- High frequency LVPECL output: 10 MHz - 200 MHz, 1 ppb step

- Low frequency LVCMOS output: 2 kHz - 125 MHz 1.8V, 2.5V and 3.3V operation

- Very-low frequency feedback clock output for connection to ToPSync® or external PFD

- Tunable over +/- 500 ppm range without loss of lock

- Integrated VCO, PFD and loop filter

- 2.3 - 2.7 GHz VCO frequency

- Typical RMS jitter performance for target application masks: OC-48, ST