LH5324C00

Key Features

- 1,572,864 × 16 bit organization

- Access time: 120 ns (MAX.)

- Supply current: - Operating: 80 mA (MAX.) - Standby: 100 µA (MAX.)

- TTL compatible I/O

- Three-state output

- Single +5 V Power supply

- Static operation

- When the address input at both A19 and A20 is high level, outputs become high impedance irrespective of CE or OE.

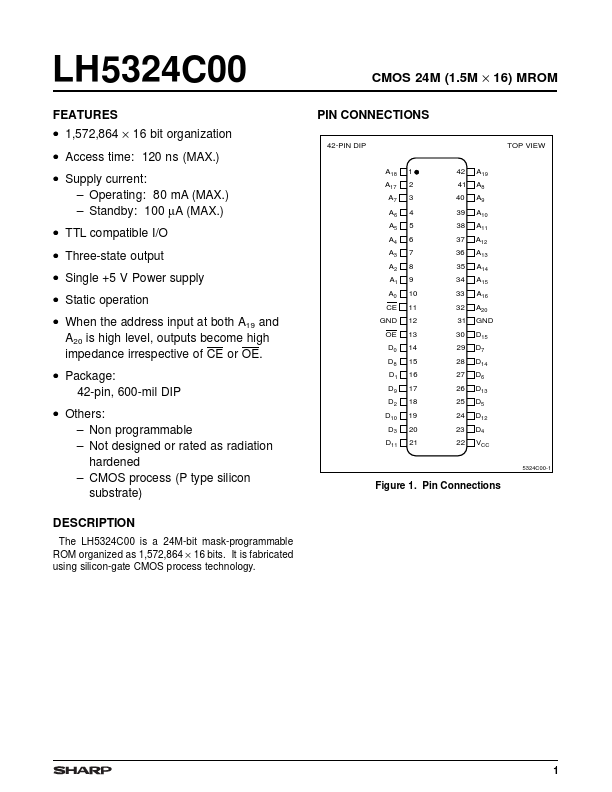

- Package: 42-pin, 600-mil DIP

- Others: - Non programmable - Not designed or rated as radiation hardened - CMOS process (P type silicon substrate) DESCRIPTION The LH5324C00 is a 24M-bit mask-programmable ROM organized as 1,572,864 × 16 bits. It is fabricated using silicon-gate CMOS process technology.