LH5P832

Key Features

- 32,768 × 8 bit organization

- Access time: 100/120 ns (MAX.)

- Cycle time: 160/190 ns (MIN.)

- Power consumption: Operating: 357.5/303 mW Standby: 16.5 mW

- TTL compatible I/O

- 256 refresh cycle/4 ms

- Auto refresh is executed by internal counter (controlled by OE/RFSH pin)

- Self refresh is executed by internal timer

- Single +5 V power supply

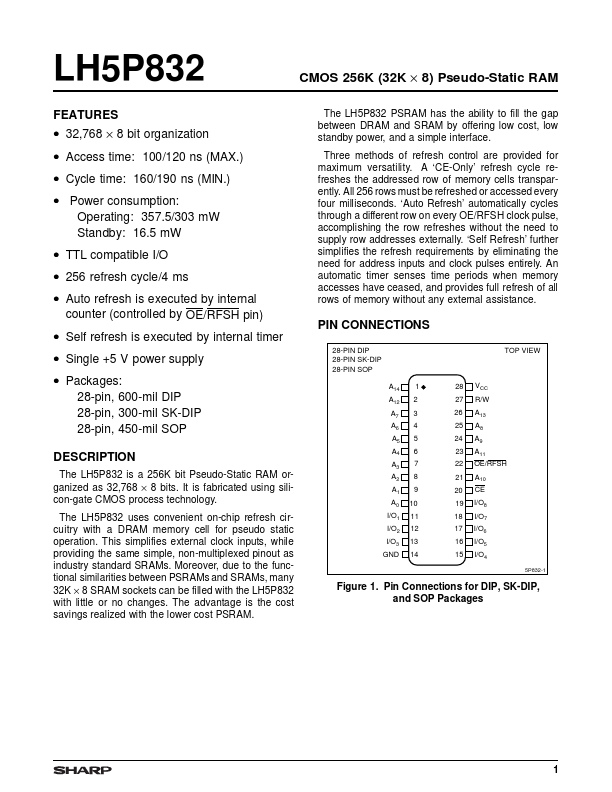

- Packages: 28-pin, 600-mil DIP 28-pin, 300-mil SK-DIP 28-pin, 450-mil SOP DESCRIPTION The LH5P832 is a 256K bit Pseudo-Static RAM organized as 32,768 × 8 bits. It is fabricated using silicon-gate CMOS process technology. The LH5P832 uses convenient on-chip refresh circuitry with a DRAM memory cell for pseudo static operation. This simplifies external clock inputs, while providing the same simple, non-multiplexed pinout as industry standard SRAMs. Moreover, due to the functional similarities between PSRAMs and SRAMs, many 32K × 8 SRAM sockets can be filled with the LH5P832 with little or no changes. The advantage is the cost savings realized with the lower cost PSRAM.