LH5P860

Description

The LH5P860 is a 512K-bit Pseudo-Static RAM organized as 65,536 × 8 bits. It is fabricated using silicon-gate CMOS process technology.

Key Features

- 65,536 × 8 bit organization

- Access time: 80 ns (MAX.)

- Cycle time: 140 ns (MIN.)

- Single +5 V power supply

- Pin compatible with 1M standard SRAM

- Power consumption (MAX.): Operating: 440 mW Self refresh (TTL level): 5.5 mW Self refresh (CMOS level): 2.75 mW

- TTL compatible I/O

- 512 refresh cycles/8 ms (MAX.)

- Available for auto-refresh and self-refresh modes

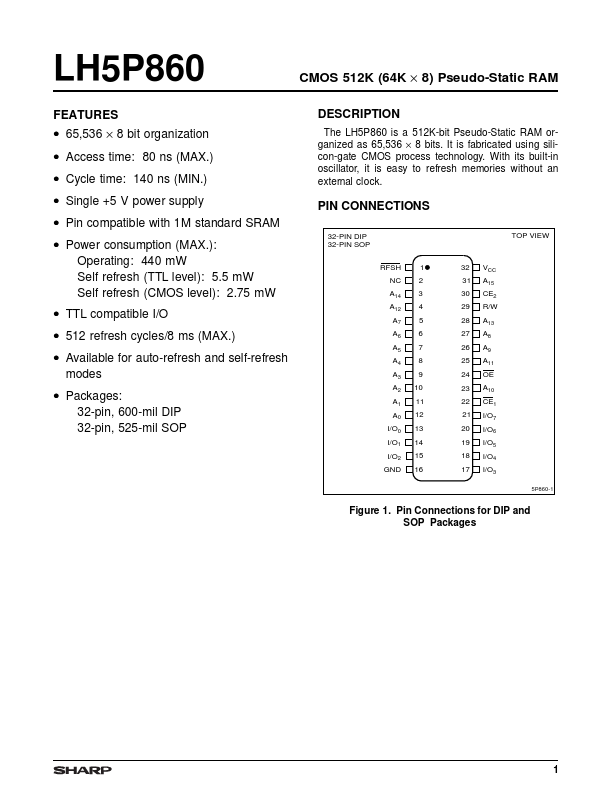

- Packages: 32-pin, 600-mil DIP 32-pin, 525-mil SOP