LH5PV16256

Description

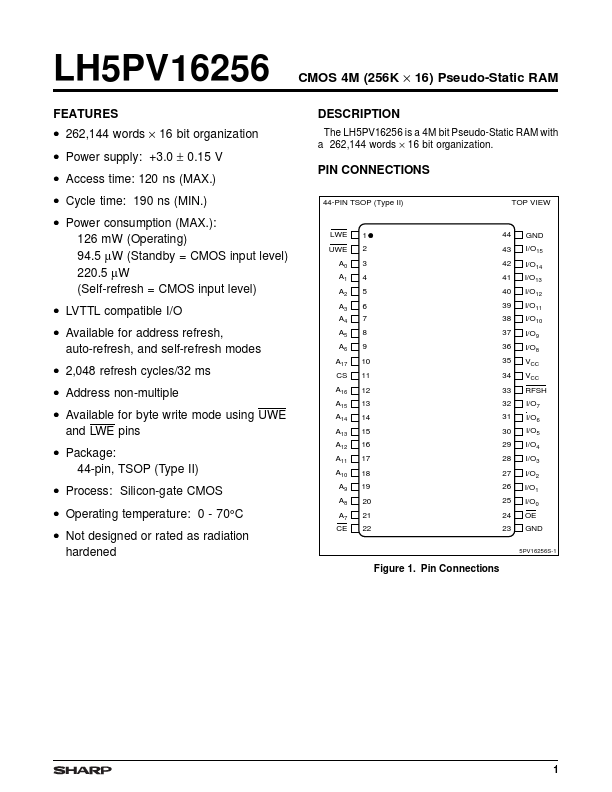

The LH5PV16256 is a 4M bit Pseudo-Static RAM with a 262,144 words × 16 bit organization. PIN CONNECTIONS 44-PIN TSOP (Type II) TOP VIEW LWE UWE A0 A1 A2 A3 A4 A5 A6 A17 CS A16 A15 A14 A13 A12 A11 A10 A9 A8 A7 CE 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 GND I/O15 I/O14 I/O13 I/O12 I/O11 I/O10 I/O9 I/O8 VCC VCC RFSH I/O7 I/O6 I/O5 I/O4 I/O3 I/O2 I/O1 I/O0 OE GND 5PV16256S-1.

Key Features

- 262,144 words × 16 bit organization

- Power supply: +3.0 ± 0.15 V

- Access time: 120 ns (MAX.)

- Cycle time: 190 ns (MIN.)

- Power consumption (MAX.): 126 mW (Operating) 94.5 µW (Standby = CMOS input level) 220.5 µW (Self-refresh = CMOS input level)

- LVTTL compatible I/O

- Available for address refresh, auto-refresh, and self-refresh modes

- 2,048 refresh cycles/32 ms

- Address non-multiple

- Available for byte write mode using UWE and LWE pins