LH5PV8512

Description

The LH5PV8512 is a 4M bit Pseudo-Static RAM with a 524,288 word × 8 bit organization. It is fabricated using silicon-gate CMOS process technology.

Key Features

- 524,288 words × 8 bit organization

- CE access time (tCEA): 120 ns (MAX.)

- Cycle time (tRC): 190 ns (MIN.)

- Power supply: +3.0 V ± 0.15 V (Operating) +2.2 V to +3.15 V (Data retention)

- Power consumption (MAX.): 126 mW (Operating) 95 µW (Standby = CMOS input level) 221 µW (Self-refresh = CMOS input level)

- Available for address refresh, auto-refresh, and self-refresh modes

- 2,048 refresh cycles/32 ms

- Address non-multiple

- Not designed or rated as radiation hardened

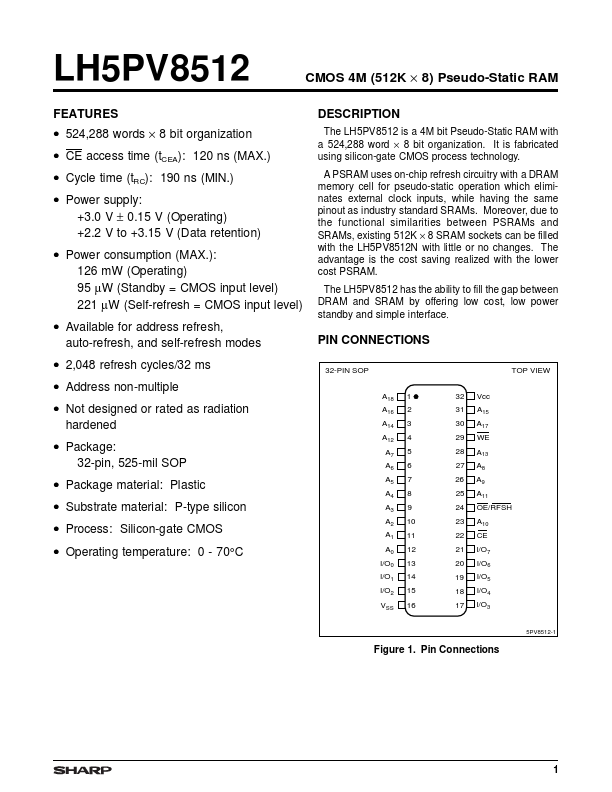

- Package: 32-pin, 525-mil SOP