HYB3117405BJ-60

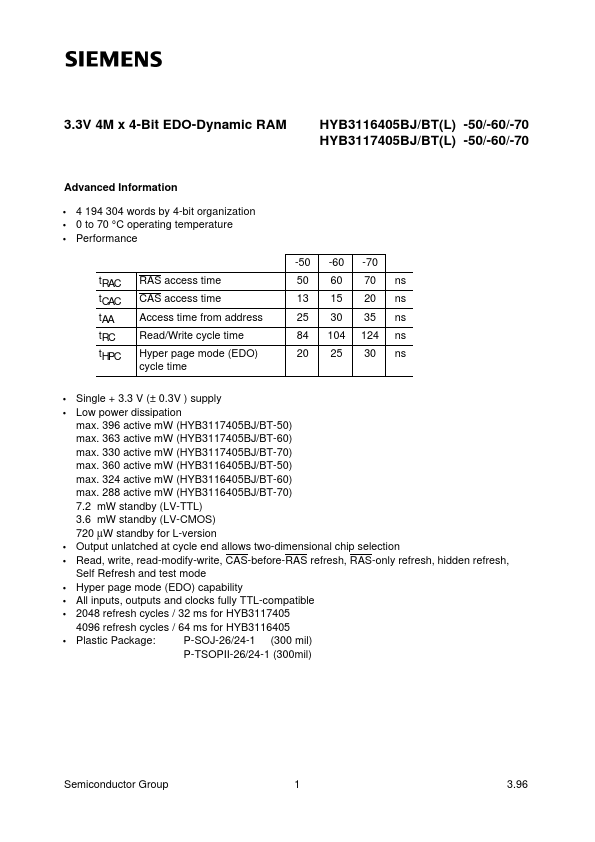

features include single + 3.3 V (± 0.3 V) power supply, direct interfacing with high-performance logic device families.The HYB3116405BTL parts have a very low power „sleep mode“ supported by Self Refresh.

Ordering Information Type

HYB 3117405BJ-50 HYB 3117405BJ-60 HYB 3117405BJ-70 HYB 3117405BT-50 HYB 3117405BT-60 HYB 3117405BT-70 HYB 3116405BJ-50 HYB 3116405BJ-60 HYB 3116405BJ-70 HYB 3116405BT-50 HYB 3116405BT-60 HYB 3116405BT-70 HYB 3116405BTL-50 HYB 3116405BTL-60 HYB 3116405BTL-70 Q67100-Q1143 Q67100-Q1144 Q67100-Q1186 on request on request on request Q67100-Q1135 Q67100-Q1136 Q67100-Q1184 Q67100-Q1127 Q67100-Q1128

Ordering Code

Q67100-Q1119 Q67100-Q1120

Package

P-SOJ-26/24-1 300 mil P-SOJ-26/24-1 300 mil P-SOJ-26/24-1 300 mil P-TSOPII-26/24-1 300 mil P-TSOPII-26/24-1 300 mil P-TSOPII-26/24-1 300 mil P-SOJ-26/24-1 300 mil P-SOJ-26/24-1 300 mil P-SOJ-26/24-1 300 mil P-TSOPII-26/24-1 300 mil P-TSOPII-26/24-1 300 mil P-TSOPII-26/24-1 300 mil P-TSOPII-26/24-1 300 mil P-TSOPII-26/24-1...