HYB39S64400

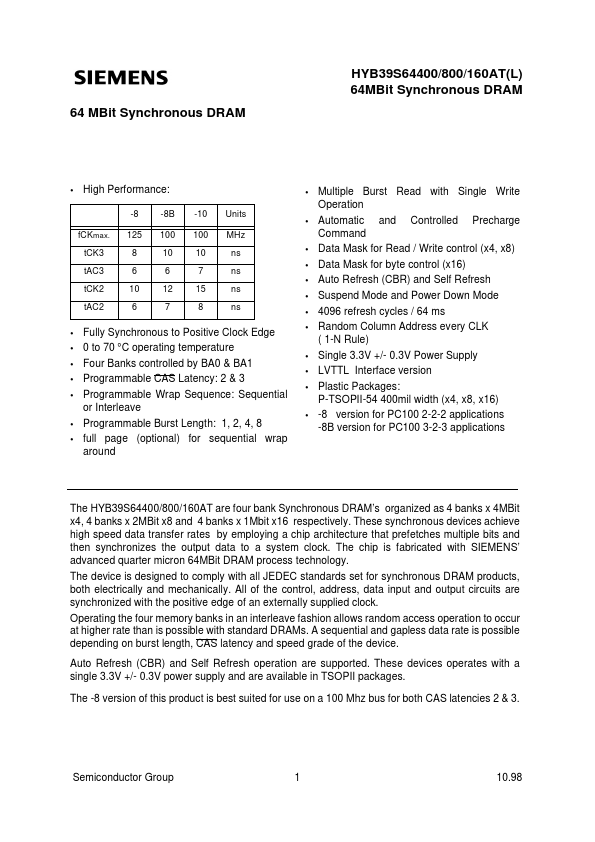

HYB39S64400 is 64M-Bit Synchronous DRAM manufactured by Siemens Semiconductor Group.

Description

LVTTL-version:

HYB 39S64400AT-8 HYB 39S64400AT-8B HYB 39S64400AT-10 HYB 39S64800AT-8 HYB 39S64800AT-8B HYB 39S64800AT-10 HYB 39S64160AT-8 HYB 39S64160AT-8B HYB 39S64160AT-10 HYB 39S64xxx0ATL-8/-10 P-TSOP-54-2 (400mil) P-TSOP-54-2 (400mil) P-TSOP-54-2 (400mil) P-TSOP-54-2 (400mil) P-TSOP-54-2 (400mil) P-TSOP-54-2 (400mil) P-TSOP-54-2 (400mil) P-TSOP-54-2 (400mil) P-TSOP-54-2 (400mil) P-TSOP-54-2 (400mil) 4B x 4M x 4 SDRAM PC100-222 4B x 4M x 4 SDRAM PC100-323 4B x 4M x 4 SDRAM PC66-222 4B x 2M x 8 SDRAM PC100-222 4B x 2M x 8 SDRAM PC100-323 4B x 2M x 8 SDRAM PC66-222 4B x 1M x 16 SDRAM PC100-222 4B x...