HYB514100BJ-60

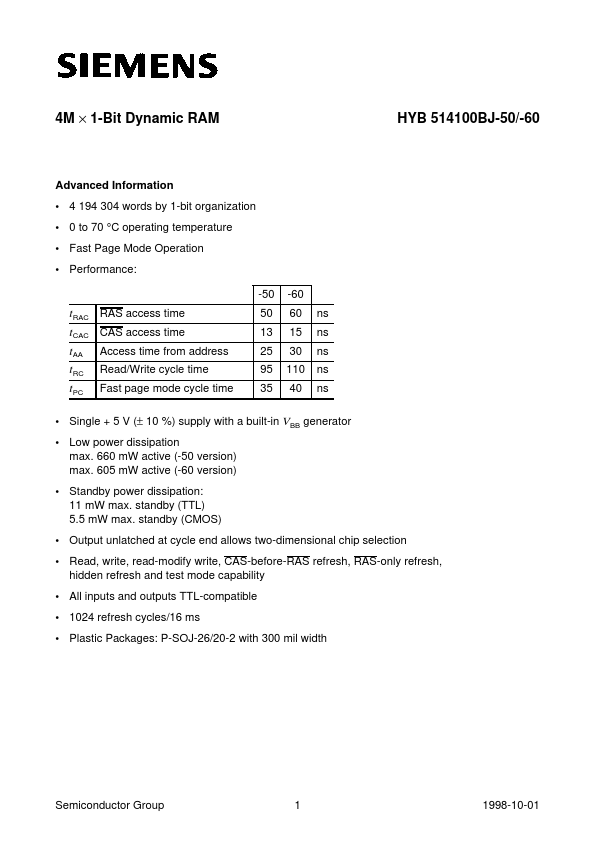

features include single + 5 V (± 10 %) power supply, direct interfacing with high performance logic device families such as Schottky TTL. Type HYB 514100BJ-50 HYB 514100BJ-60 Ordering Code Q67100-Q971 Q67100-Q759 Package P-SOJ-26/20-2 300 mil P-SOJ-26/20-2 300 mil Descriptions DRAM (access time 50 ns) DRAM (access time 60 ns)

P-SOJ-26/20-2

V SS DO CAS N.C. A9

DI WE RAS N.C. A10

1 2 3 4 5

26 25 24 23 22

A0 A1 A2 A3 V CC

9 10 11 12 13

18 17 16 15 14

A8 A7 A6 A5 A4

SPP02808

Pin Configuration Pin Names A0

- A10 RAS CAS WE DI DO Address Input Row Address Strobe Column Address Strobe Read/Write Input Data In Data Out Power Supply (+ 5 V) Ground (0 V) No Connection

VCC VSS

N.C.

Semiconductor Group

1998-10-01

HYB 514100BJ-50/-60 4M × 1 DRAM

WE CAS

&

Data In Buffer

No.2 Clock Generator

Data Out Buffer

11 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 11

Column Address Buffers (11)

11 Column Decoder

Refresh Controller

Sense Amplifier I/O Gating

Refresh Counter (10) 10 Row...