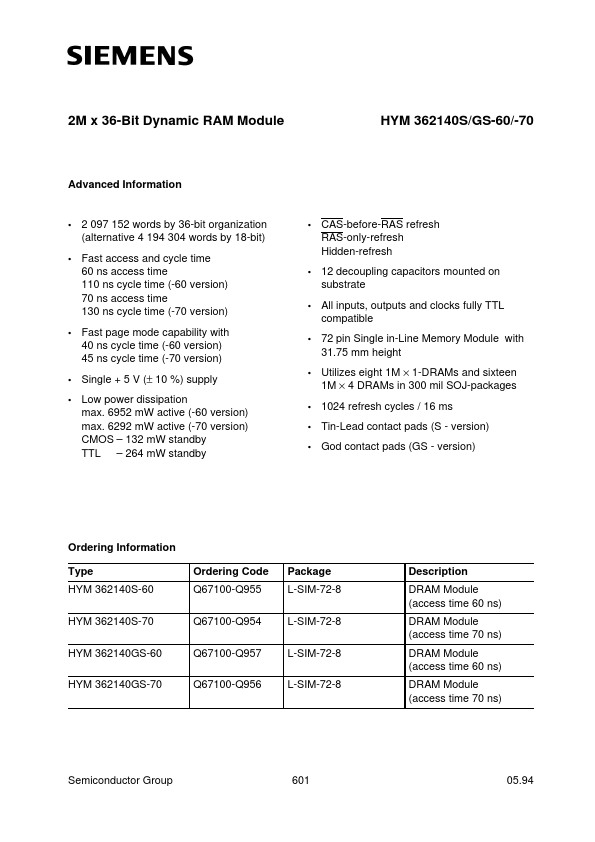

HYM362140S

Description

DRAM Module (access time 60 ns) DRAM Module (access time 70 ns) DRAM Module (access time 60 ns) DRAM Module (access time 70 ns)

Semiconductor Group

HYM 362140S/GS-60/-70 2M x 36-Bit

The HYM 362140S/GS-60/-70 is a 8 M Byte DRAM module organized as 2 097 152 words by 36-bit in a 72-pin single-in-line package prising eight HYB 511000BJ 1M × 1 DRAMs and sixteen HYB 514400BJ 1M × 4 DRAMs in 300 mil wide SOJ-packages mounted together with twelve 0.2 µF ceramic decoupling capacitors on a PC board. The HYM 362140S/GS-60/-70 can also be used as a 4 194 304 words by 18-bits dynamic RAM module by means of connecting DQ0 and DQ18, DQ1 and DQ19, DQ2 and DQ20, …, DQ17 and DQ35, respectively. Each HYB 511000BJ and HYB 514400BJ is described in the data sheet and is fully electrical tested and processed according to SIEMENS standard quality procedure prior to module assembly. After assembly onto the board, a further set of electrical tests is performed. The speed of the...