HYM72V2005GS-50

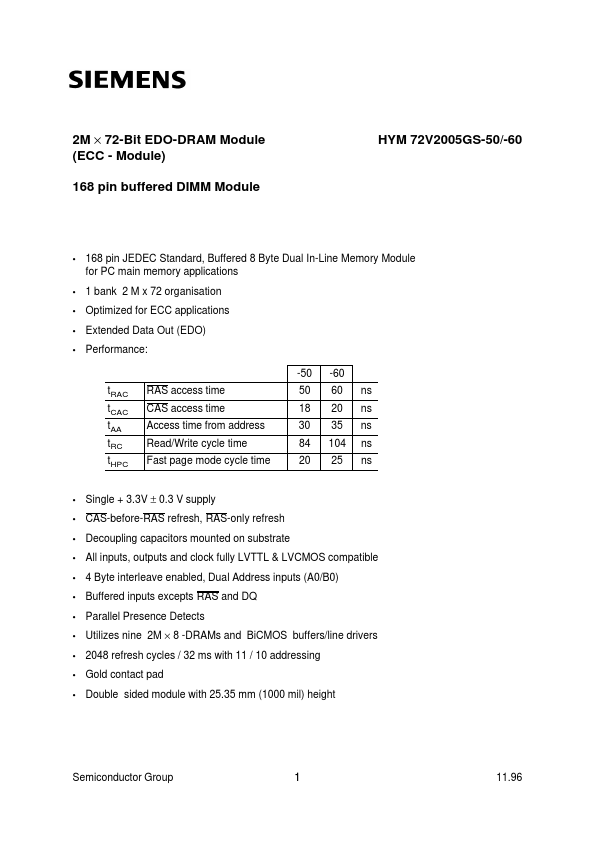

2M × 72-Bit EDO-DRAM Module (ECC

- Module) 168 pin buffered DIMM Module

HYM 72V2005GS-50/-60

- 168 pin JEDEC Standard, Buffered 8 Byte Dual In-Line Memory Module for PC main memory applications 1 bank 2 M x 72 organisation Optimized for ECC applications Extended Data Out (EDO) Performance: -50 t RAC t CAC t AA t RC t HPC RAS access time CAS access time Access time from address Read/Write cycle time Fast page mode cycle time 50 18 30 84 20 -60 60 20 35 104 25 ns ns ns ns ns

- -

- -

- -

- -

- -

- -

- -

- Single + 3.3V ± 0.3 V supply CAS-before-RAS refresh, RAS-only refresh Decoupling capacitors mounted on substrate All inputs, outputs and clock fully LVTTL & LVCMOS patible 4 Byte interleave enabled, Dual Address inputs (A0/B0) Buffered inputs excepts RAS and DQ Parallel Presence Detects Utilizes nine 2M × 8 -DRAMs and Bi CMOS buffers/line drivers 2048 refresh cycles / 32 ms with 11 / 10 addressing Gold contact pad Double sided module with 25.35 mm (1000 mil) height

Semiconductor...