HYS64V8000GU

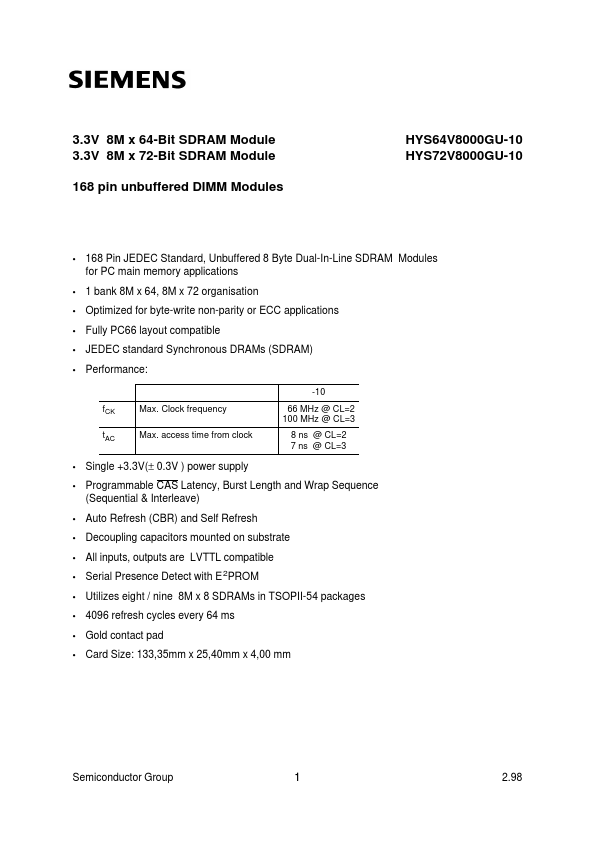

3.3V 8M x 64-Bit SDRAM Module 3.3V 8M x 72-Bit SDRAM Module 168 pin unbuffered DIMM Modules

HYS64V8000GU-10 HYS72V8000GU-10

- 168 Pin JEDEC Standard, Unbuffered 8 Byte Dual-In-Line SDRAM Modules for PC main memory applications 1 bank 8M x 64, 8M x 72 organisation Optimized for byte-write non-parity or ECC applications Fully PC66 layout patible JEDEC standard Synchronous DRAMs (SDRAM) Performance:

-10 f CK t AC Max. Clock frequency Max. access time from clock 66 MHz @ CL=2 100 MHz @ CL=3 8 ns @ CL=2 7 ns @ CL=3

- -

- -

- -

- Single +3.3V(± 0.3V ) power supply Programmable CAS Latency, Burst Length and Wrap Sequence (Sequential & Interleave) Auto Refresh (CBR) and Self Refresh Decoupling capacitors mounted on substrate All inputs, outputs are LVTTL patible Serial Presence Detect with E 2PROM Utilizes eight / nine 8M x 8 SDRAMs in TSOPII-54 packages 4096 refresh cycles every 64 ms Gold contact pad Card Size: 133,35mm x 25,40mm x 4,00 mm

- -

- -

- -

- -

Semiconductor...