HYS72V1000GU-50

3.3V 1M x 64-Bit SDRAM Module 3.3V 1M x 72-Bit SDRAM Module 168 pin unbuffered DIMM Modules

HYS64V1000GS-10/-12/-15 HYS72V1000GS-10/-12/-15

Target Information

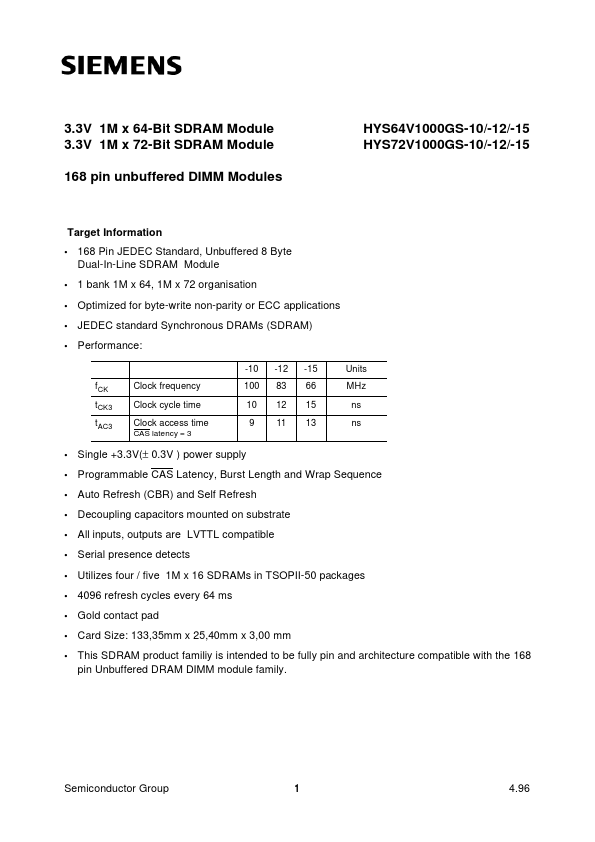

- 168 Pin JEDEC Standard, Unbuffered 8 Byte Dual-In-Line SDRAM Module 1 bank 1M x 64, 1M x 72 organisation Optimized for byte-write non-parity or ECC applications JEDEC standard Synchronous DRAMs (SDRAM) Performance:

-10 f CK t CK3 t AC3 Clock frequency Clock cycle time Clock access time

CAS latency = 3

- -

- -

-12 83 12 11

-15 66 15 13

Units MHz ns ns

100 10 9

- -

- -

- -

- -

- -

- Single +3.3V(± 0.3V ) power supply Programmable CAS Latency, Burst Length and Wrap Sequence Auto Refresh (CBR) and Self Refresh Decoupling capacitors mounted on substrate All inputs, outputs are LVTTL patible Serial presence detects Utilizes four / five 1M x 16 SDRAMs in TSOPII-50 packages 4096 refresh cycles every 64 ms Gold contact pad Card Size: 133,35mm x 25,40mm x 3,00 mm This SDRAM product familiy is intended to be fully pin and...