82S25 Overview

Description

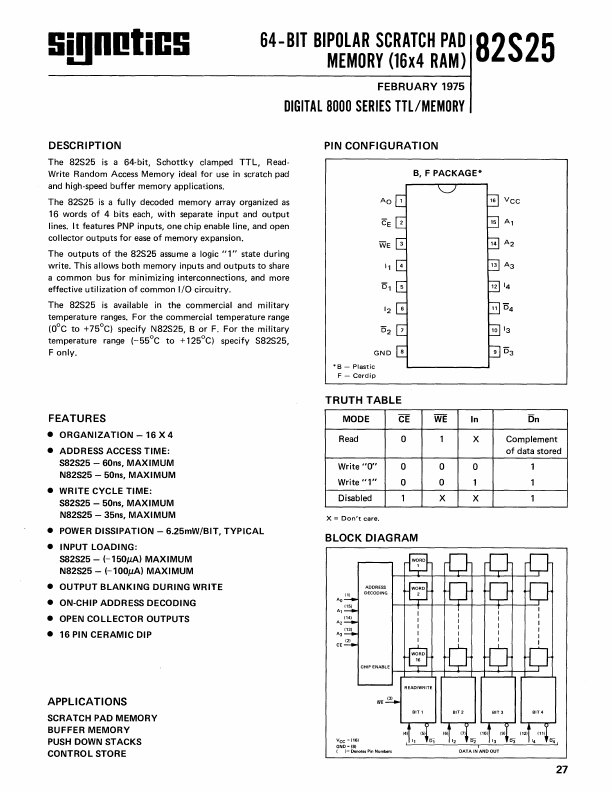

The 82S25 is a 64-bit, Schottky clamped TTL, ReadWrite Random Access Memory ideal for use in scratch pad and high-speed buffer memory applications. The 82S25 is a fu lIy decoded memory array organ ized as 16 words of 4 bits each, with separate input and output lines.

Key Features

- ORGANIZATION -16 X 4

- ADDRESS ACCESS TIME: S82S25 - 60ns, MAXIMUM N82S25 - 50ns, MAXIMUM

- WRITE CYCLE TIME: S82S25 - 50ns, MAXIMUM N82S25 - 35ns, MAXIMUM

- POWER DISSIPATION

- 6.25mW/BIT, TYPICAL

- INPUT LOADING: S82S25 - (-150tLA) MAXIMUM N82S25 - (-100JlA) MAXI MUM

- OUTPUT BLANKING DURING WRITE

- ON-CHIP ADDRESS DECODING

- OPEN COLLECTOR OUTPUTS

- 16 PIN CERAMIC DIP