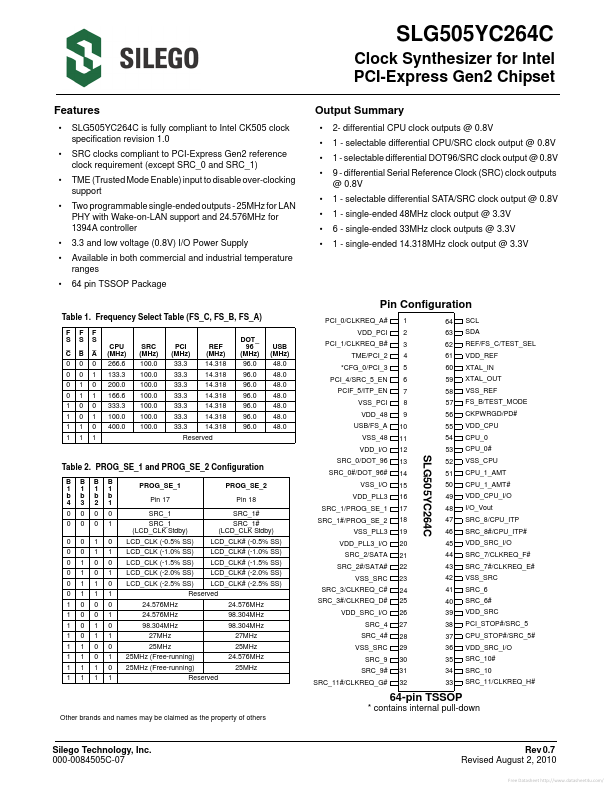

SLG505YC264C

SLG505YC264C is manufactured by Silego.

Clock Synthesizer for Intel PCI-Express Gen2 Chipset

Features

- -

- - SLG505YC264C is fully pliant to Intel CK505 clock specification revision 1.0 SRC clocks pliant to PCI-Express Gen2 reference clock requirement (except SRC_0 and SRC_1) TME (Trusted Mode Enable) input to disable over-clocking support Two programmable single-ended outputs

- 25MHz for LAN PHY with Wake-on-LAN support and 24.576MHz for 1394A controller 3.3 and low voltage (0.8V) I/O Power Supply Available in both mercial and industrial temperature ranges 64 pin TSSOP Package

Output Summary

- -

- -

- -

- - 2- differential CPU clock outputs @ 0.8V 1

- selectable differential CPU/SRC clock output @ 0.8V 1...