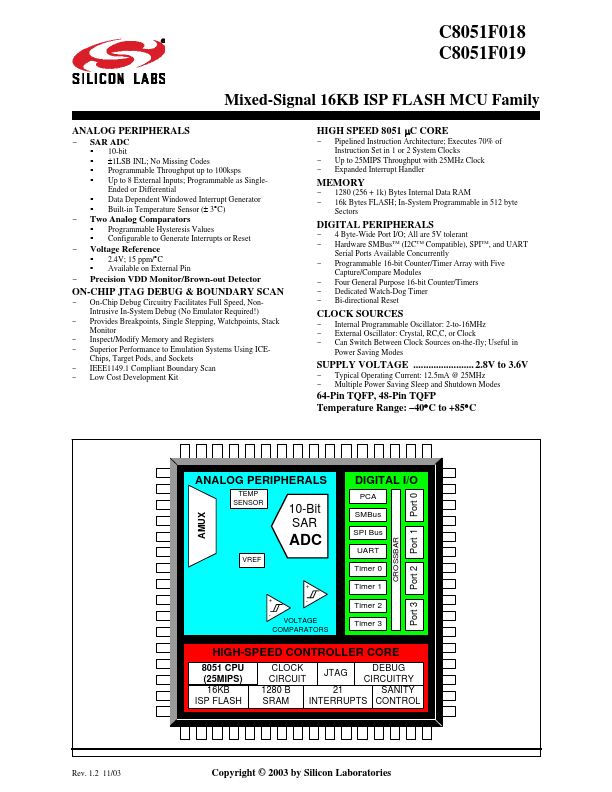

| Part | C8051F018 |

|---|---|

| Description | Mixed-Signal 16KB ISP FLASH MCU |

| Manufacturer | Silicon Labs |

| Size | 732.24 KB |

Related Datasheets

- STM32F103C8T6 — STMicroelectronics — ARM-based 32-bit MCU

- STM32F103 — STMicroelectronics — ARM-based 32-bit MCU

- MC96F8208S — ABOV — CMOS single-chip 8-bit MCU