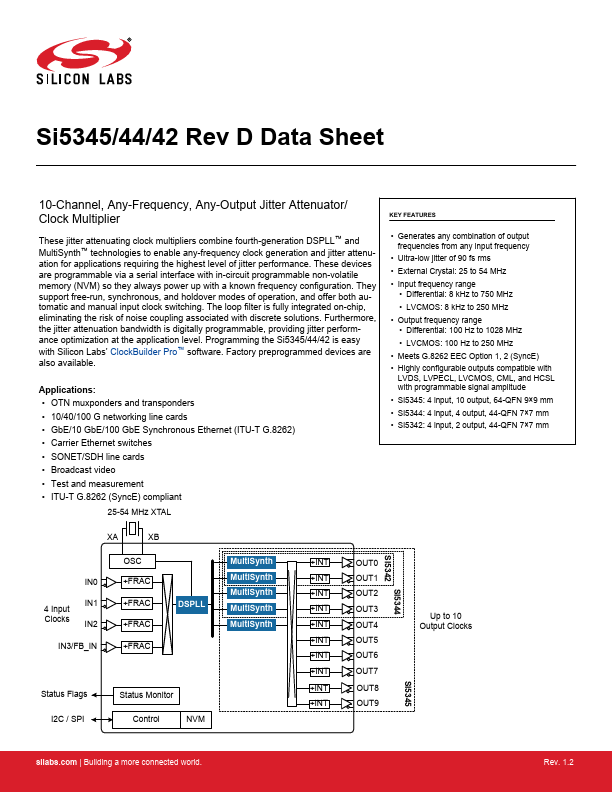

SI5344

Overview

- Generates any combination of output

- frequencies from any input frequency *

- Input frequency range:

- Differential: 8 kHz to 750 MHz *

- LVCMOS: 8 kHz to 250 MHz

- Output frequency range: *

- Differential: up to 712.5 MHz *

- LVCMOS: up to 250 MHz

- Ultra-low jitter: <100 fs typ (12 kHz-20 MHz)

- Programmable jitter attenuation