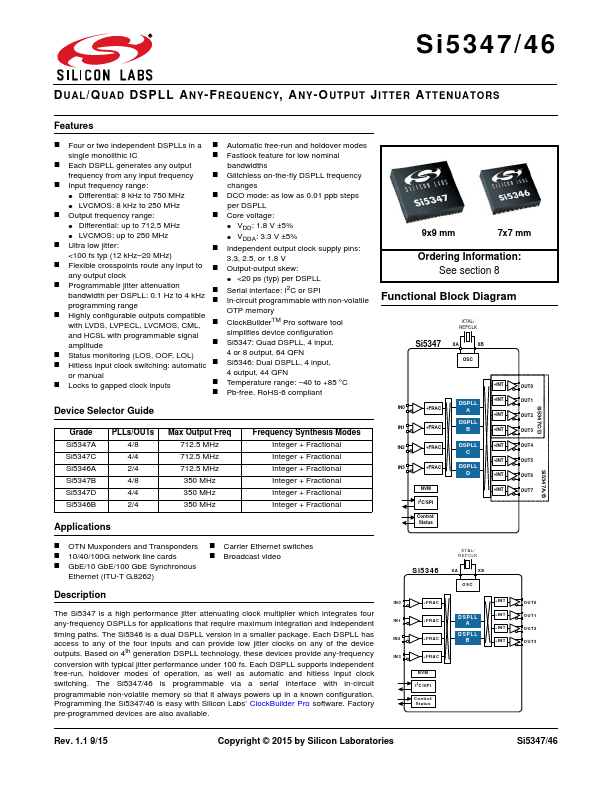

SI5346 Overview

Key Features

- Four or two independent DSPLLs in a

- Fastlock feature for low nominal

- Each DSPLL generates any output bandwidths frequency from any input frequency

- Input frequency range

- Glitchless on-the-fly DSPLL frequency changes

- Differential: 8 kHz to 750 MHz

- DCO mode: as low as 0.01 ppb steps

- LVCMOS: 8 kHz to 250 MHz

- Output frequency range: per DSPLL

- Core voltage