Si5321

Si5321 is SONET/SDH PRECISION CLOCK MULTIPLIER IC manufactured by Silicon Labs.

Features

- Ultra-low jitter clock output with jitter

- Digital hold for loss-of-input clock generation as low as 0.3 ps RMS

- Support for 255/238 (15/14),

- No external ponents (other than a 255/237 (85/79), and 66/64 FEC scaling resistor and bypassing)

(ITU-T G.709 and IEEE 802.3ae)

- Input clock ranges at 19, 39, 78, 155,

- Selectable loop bandwidth

311, or 622 MHz

- Loss-of-signal alarm output

- Output clock ranges at 19, 39, 78, 155,

- Low power

311, 622, 1244, or 2488 MHz

- Small size (9 x 9 mm)

- Maximum range includes 693 MHz for

- Backwards patible with Si5320

10 Gb E FEC support

Applications

- SONET/SDH line/port cards

- Terabit routers

- Core switches

- Digital cross connects

Description

The Si5321 is a precision clock multiplier that exceeds the requirements of high-speed munication systems, including OC-192/OC-48 and 10 Gigabit Ethernet. This device phase locks to an input clock in the 19, 39, 78, 155, 311 or 622 MHz frequency range and generates a frequency-multiplied clock output that can be configured for operation in the 19, 39, 78, 155, 622, 1244, or 2488 MHz frequency range. Silicon Laboratories DSPLL® technology provides PLL functionality with unparalleled performance. It eliminates external loop filter ponents, provides programmable loop parameters, and simplifies design. FEC rates are supported by selectable forward and reverse 255/ 238 (15/14), 255/237 (85/79), and 66/64 (33/32) conversion factors. The ITU-T G.709 255/237 rate and the IEEE 802.3ae 66/64 rate are supported when using a 155 MHz or higher rate input clock. The performance and integration of Silicon Laboratories’ Si5321 clock IC provides high-level support of the latest specifications and systems. It operates from a single 3.3 V supply.

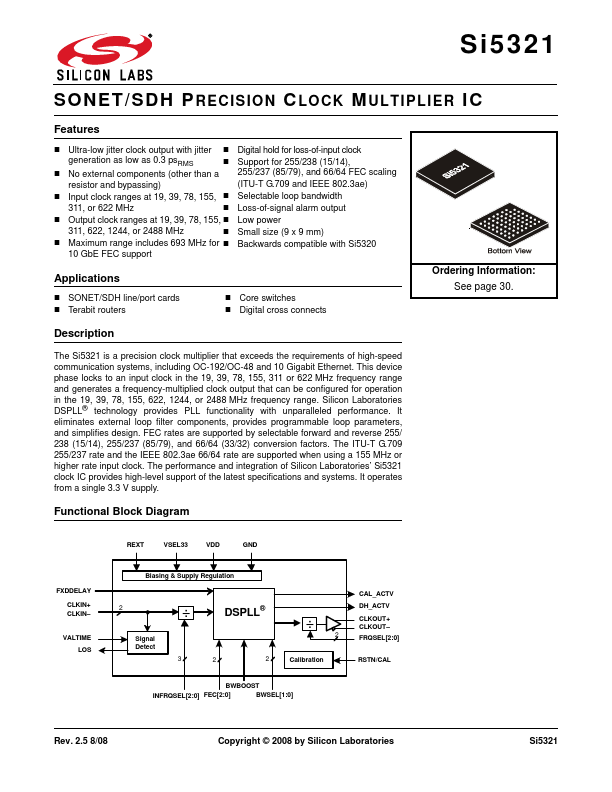

Functional Block Diagram

Si5321 Si5321

Ordering Information: See page 30.

REXT

VSEL33

FXDDELAY CLKIN+ CLKIN-

VALTIME LOS

Biasing & Supply Regulation

2 ÷ DSPLL®

Signal...