Si5350C

Overview

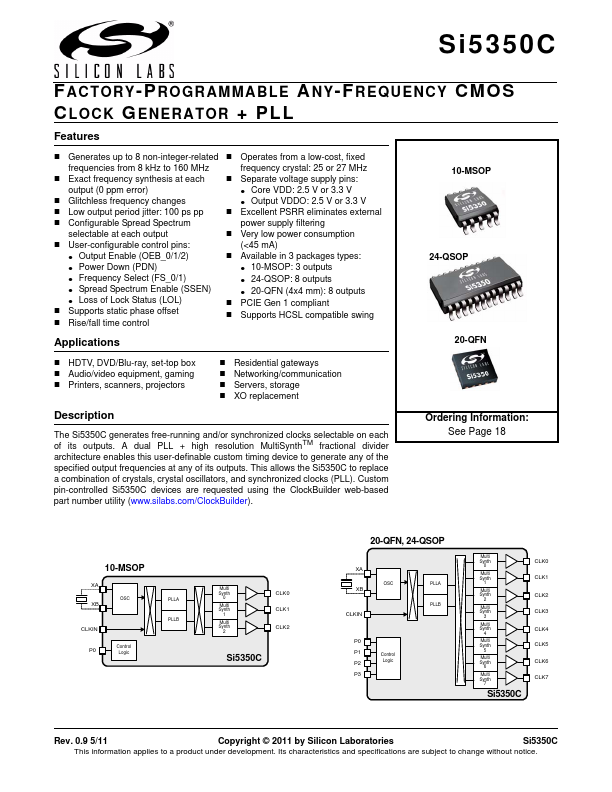

The Si5350C generates free-running and/or synchronized clocks selectable on each of its outputs. A dual PLL + high resolution MultiSynthTM fractional divider architecture enables this user-definable custom timing device to generate any of the specified output frequencies at any of its outputs.

- Generates up to 8 non-integer-related

- Operates from a low-cost, fixed frequencies from 8 kHz to 160 MHz frequency crystal: 25 or 27 MHz

- Exact frequency synthesis at each

- Separate voltage supply pins: output (0 ppm error)

- Core VDD: 2.5 V or 3.3 V

- Glitchless frequency changes

- Output VDDO: 2.5 V or 3.3 V

- Low output period jitter: 100 ps pp

- Excellent PSRR eliminates external

- Configurable Spread Spectrum power supply filtering selectable at each output