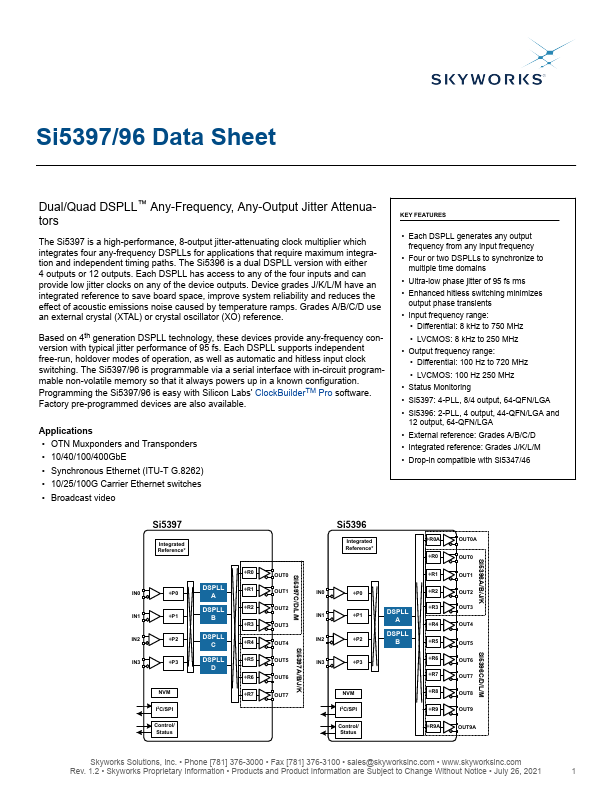

Si5396

Overview

- Each DSPLL generates any output frequency from any input frequency

- Four or two DSPLLs to synchronize to multiple time domains

- Ultra-low phase jitter of 95 fs rms

- Enhanced hitless switching minimizes output phase transients

- Input frequency range:

- Differential: 8 kHz to 750 MHz

- LVCMOS: 8 kHz to 250 MHz

- Output frequency range:

- Differential: 100 Hz to 720 MHz

- LVCMOS: 100 Hz 250 MHz