49LF002

Overview

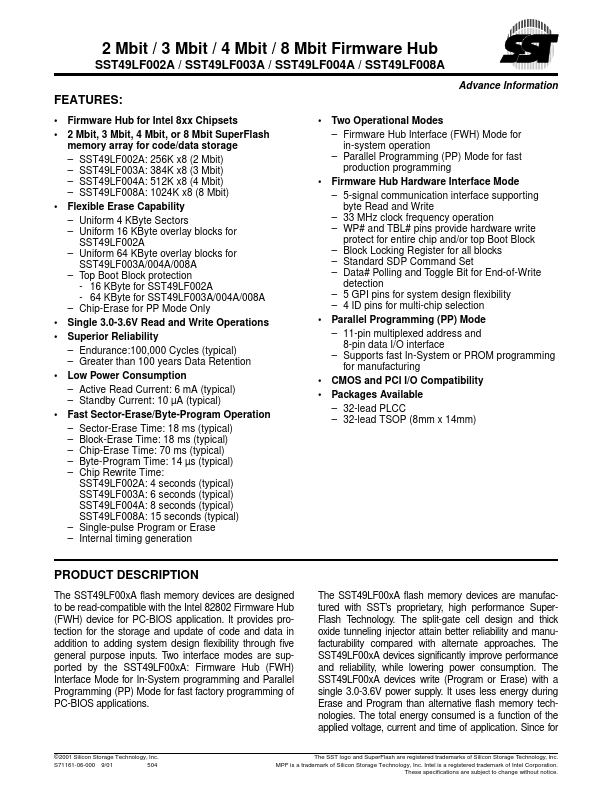

- Firmware Hub for Intel 8xx Chipsets

- 2 Mbit, 3 Mbit, 4 Mbit, or 8 Mbit SuperFlash memory array for code/data storage - SST49LF002A: 256K x8 (2 Mbit) - SST49LF003A: 384K x8 (3 Mbit) - SST49LF004A: 512K x8 (4 Mbit) - SST49LF008A: 1024K x8 (8 Mbit)

- Flexible Erase Capability - Uniform 4 KByte Sectors - Uniform 16 KByte overlay blocks for SST49LF002A - Uniform 64 KByte overlay blocks for SST49LF003A/004A/008A - Top Boot Block protection - 16 KByte for SST49LF002A - 64 KByte for SST49LF003A/004A/008A - Chip-Erase for PP Mode Only

- Single 3.0-3.6V Read and Write Operations

- Superior Reliability - Endurance:100,000 Cycles (typical) - Greater than 100 years Data Retention

- Low Power Consumption - Active Read Current: 6 mA (typical) - Standby Current: 10 µA (typical)

- Fast Sector-Erase/Byte-Program Operation - Sector-Erase Time: 18 ms (typical) - Block-Erase Time: 18 ms (typical) - Chip-Erase Time: 70 ms (typical) - Byte-Program Time: 14 µs (typical) - Chip Rewrite Time: SST49LF002A: 4 seconds (typical) SST49LF003A: 6 seconds (typical) SST49LF004A: 8 seconds (typical) SST49LF008A: 15 seconds (typical) - Single-pulse Program or Erase - Internal timing generation

- Two Operational Modes - Firmware Hub Interface (FWH) Mode for in-system operation - Parallel Programming (PP) Mode for fast production programming

- Firmware Hub Hardware Interface Mode - 5-signal communication interface supporting byte Read and Write - 33 MHz clock frequency operation - WP# and TBL# pins provide hardware write protect for entire chip and/or top Boot Block - Block Locking Register for all blocks - Standard SDP Command Set - Data# Polling and Toggle Bit for End-of-Write detection - 5 GPI pins