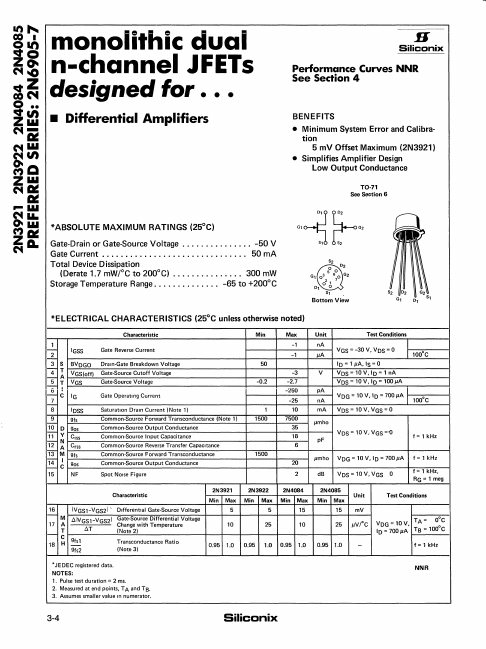

2N4084 Description

monolithic dual n-channel JFETs designed for DiHerential Amplifiers H Siliconix Performance Curves NNR See Section 4 BENEFITS Minimum System Error and Calibration 5 mV Offset Maximum (2N3921) Simplifies Amplifier Design Low Output Conductance TO-71 See Section 6 RATINGS (25°C) Gate-Drain or Gate-Source Voltage .............. -50 V Gate Current ............................... 50 rnA Total Device Dissipation (Derate...