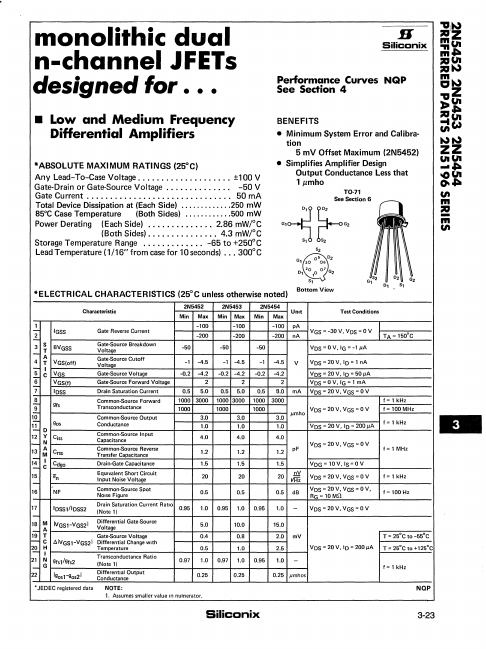

| Part | 2N5452 |

|---|---|

| Description | monolithic dual n-channel JFET |

| Manufacturer | Siliconix |

| Size | 83.74 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 2N5452 | Intersil | DUAL N-CHANNEL JFET |

| 2N5457 | Motorola Semiconductor | GENERAL PURPOSE JFET |

| 2N5459 | Motorola Semiconductor | GENERAL PURPOSE JFET |

| 2N5459 | Fairchild Semiconductor | N-Channel General Purpose Amplifier |

| 2N5453 | Intersil | DUAL N-CHANNEL JFET |