U631H64

U631H64 is SoftStore 8K x 8 nvSRAM manufactured by Simtek Corporation.

Features

High-performance CMOS nonvolatile static RAM 8192 x 8 bits

- 25, 35 and 45 ns Access Times

- 12, 20 and 25 ns Output Enable Access Times

- Software STORE Initiation (STORE Cycle Time < 10 ms)

- Automatic STORE Timing

- 105 STORE cycles to EEPROM

- 10 years data retention in .. EEPROM

- Automatic RECALL on Power Up

- Software RECALL Initiation (RECALL Cycle Time < 20 μs)

- Unlimited RECALL cycles from EEPROM

- Unlimited Read and Write to SRAM

- Single 5 V ± 10 % Operation

- Operating temperature ranges: 0 to 70 °C -40 to 85 °C

- QS 9000 Quality Standard

- ESD characterization according MIL STD 883C M3015.7-HBM (classification see IC Code Numbers)

- Ro HS pliance and Pb- free

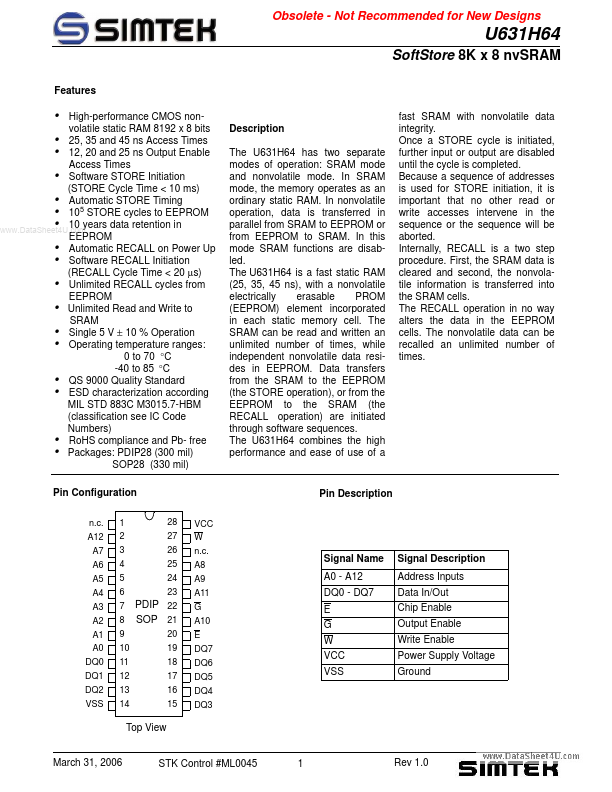

- Packages: PDIP28 (300 mil) SOP28 (330 mil) Pin Configuration n.c. A12 A7 A6 A5 A4 A3 A2 A1 A0 DQ0 DQ1 DQ2 VSS 1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 VCC W n.c. A8 A9 A11 G A10 E DQ7 DQ6 DQ5 DQ4 DQ3

- Description The U631H64 has two separate modes of operation: SRAM mode and nonvolatile mode. In SRAM mode, the memory operates as an ordinary static RAM. In nonvolatile operation, data is transferred in parallel from SRAM to EEPROM or from EEPROM to SRAM. In this mode SRAM functions are disabled. The U631H64 is a fast static RAM (25, 35, 45 ns), with a nonvolatile electrically erasable PROM (EEPROM) element incorporated in each static memory cell. The SRAM can be read and written an unlimited number of times, while independent nonvolatile data resides in EEPROM. Data transfers from the SRAM to the EEPROM (the STORE operation), or from the EEPROM to the SRAM (the RECALL operation) are initiated through software sequences. The U631H64 bines the high performance and ease of use of a fast SRAM with nonvolatile data integrity. Once a STORE cycle is initiated, further input or output are disabled until the cycle is pleted. Because a sequence of addresses is used for STORE initiation, it is important that no other read or write accesses intervene in the sequence or the sequence...