| Part | Si53328 |

|---|---|

| Description | Low-Jitter LVPECL Fanout Clock Buffers |

| Manufacturer | Skyworks Solutions |

| Size | 2.31 MB |

Pricing from 190.45 USD, available from DigiKey and Richardson RFPD.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| DigiKey | 11 | 1+ : 190.45 USD | View Offer |

| Richardson RFPD | -3 | 1+ : 193.91 USD | View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

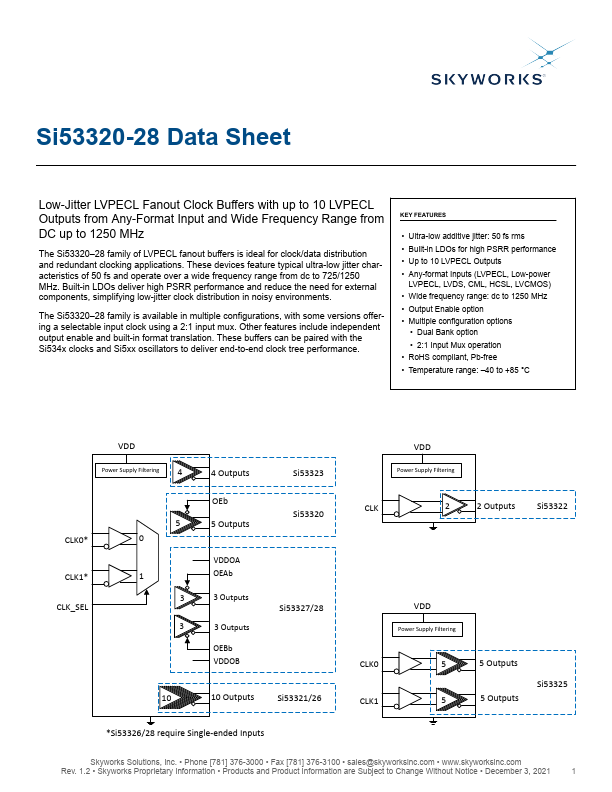

| SI53328 | Silicon Labs | Low-Jitter LVPECL Fanout Clock Buffers |

| Si5332 | Skyworks Solutions | Any-Frequency Clock Generator |

| SI53320 | Silicon Labs | Low-Jitter LVPECL Fanout Clock Buffers |

| Si5332 | Silicon Labs | 6/8/12-Output Any-Frequency Clock Generator |

| SI53323 | Silicon Labs | Low-Jitter LVPECL Fanout Clock Buffers |