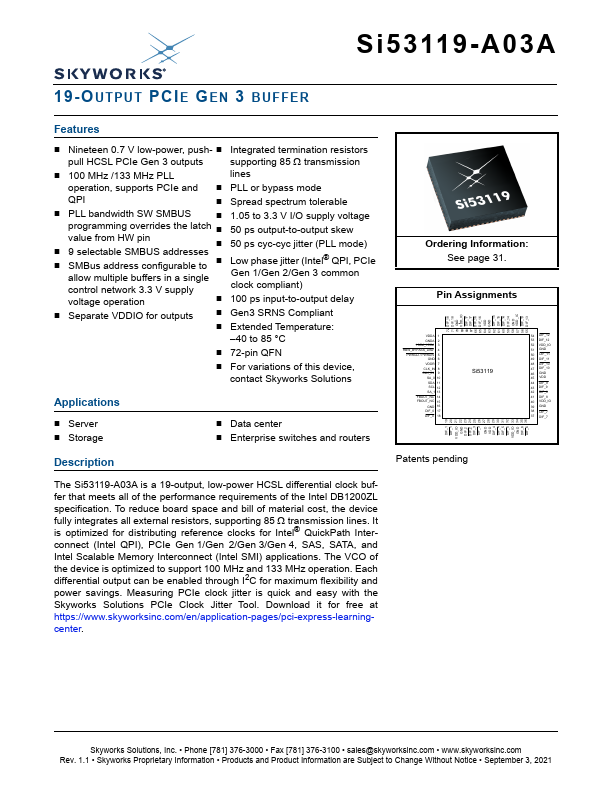

Si53119-A03A Overview

Key Specifications

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.465 V

Min Voltage (typical range): 3.135 V

Length: 10 mm

Description

The Si53119-A03A is a 19-output, low-power HCSL differential clock buffer that meets all of the performance requirements of the Intel DB1200ZL specification. To reduce board space and bill of material cost, the device fully integrates all external resistors, supporting 85 transmission lines.

Key Features

- Nineteen 0.7 V low-power, push

- Integrated termination resistors pull HCSL PCIe Gen 3 outputs supporting 85 transmission

- 100 MHz /133 MHz PLL lines operation, supports PCIe and

- PLL or bypass mode QPI

- Spread spectrum tolerable