Si5328

Si5328 is ITU-T G.8262 SYNCHRONOUS ETHERNET JITTER-ATTENUATING CLOCK MULTIPLIER manufactured by Skyworks Solutions.

Features

- Fully-pliant with ITU-T G.8262, EEC options 1 and 2.

- Generates any frequency from 8 k Hz to 808 MHz.

- Dual clock outputs with selectable signal format (LVPECL, LVDS, CML, CMOS)

- LOL, LOS, FOS alarm outputs

- Ultra-low jitter clock outputs with

- I2C or SPI programmable jitter generation as low rms (12 k Hz- 20 MHz) as

0.3 ps

- On-chip voltage regulator for 2.5 ±10% or 3.3 V ±10%

- Integrated loop filter with operation selectable loop bandwidth (0.1 Hz; 1 to 10 Hz)

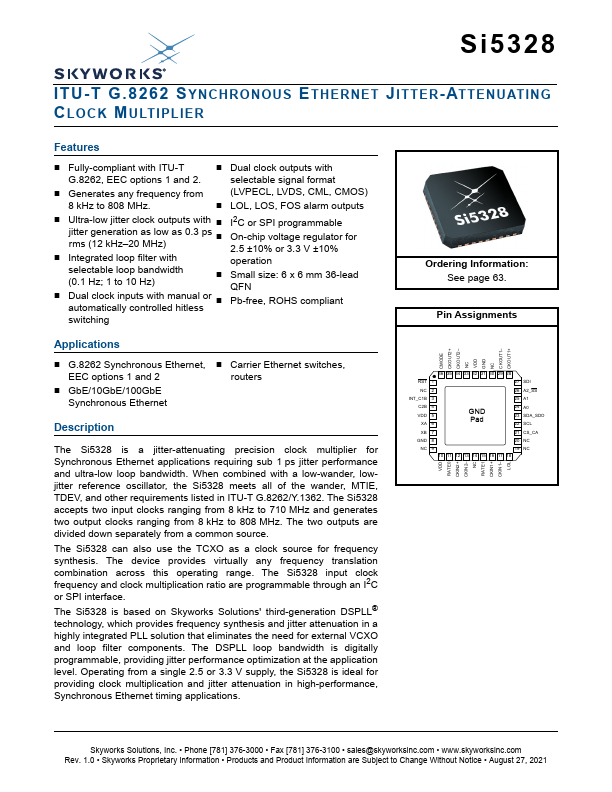

- Small size: 6 x 6 mm 36-lead QFN

- Dual clock inputs with manual or automatically controlled hitless

- Pb-free, ROHS pliant switching

Applications

- G.8262 Synchronous Ethernet, EEC options 1 and 2

- Gb E/10Gb E/100Gb E Synchronous Ethernet

- Carrier Ethernet switches, routers

Description

The Si5328 is a jitter-attenuating precision clock multiplier for Synchronous Ethernet applications requiring sub 1 ps jitter performance and ultra-low loop bandwidth. When bined with a low-wander, lowjitter reference oscillator, the Si5328 meets all of the wander, MTIE, TDEV, and other requirements listed in ITU-T G.8262/Y.1362. The Si5328 accepts two input clocks ranging from 8 k Hz to 710 MHz and generates two output clocks ranging from 8 k Hz to 808 MHz. The two outputs are divided down separately from a mon source.

The Si5328 can also use the TCXO as a clock source for frequency synthesis. The device provides virtually any frequency translation bination across this operating range. The Si5328 input clock frequency and clock multiplication ratio are programmable through an I2C or SPI interface.

The Si5328 is based on Skyworks Solutions' third-generation DSPLL® technology, which provides frequency synthesis and jitter attenuation in a highly integrated PLL solution that eliminates the need for external VCXO and loop filter ponents. The DSPLL loop bandwidth is digitally programmable, providing jitter performance optimization at the application level. Operating from a single 2.5 or 3.3 V...