CXD8302Q

CXD8302Q is PLL for CCD Cameras manufactured by Sony Semiconductor Solutions.

PLL for CCD Cameras For the availability of this product, please contact the sales office.

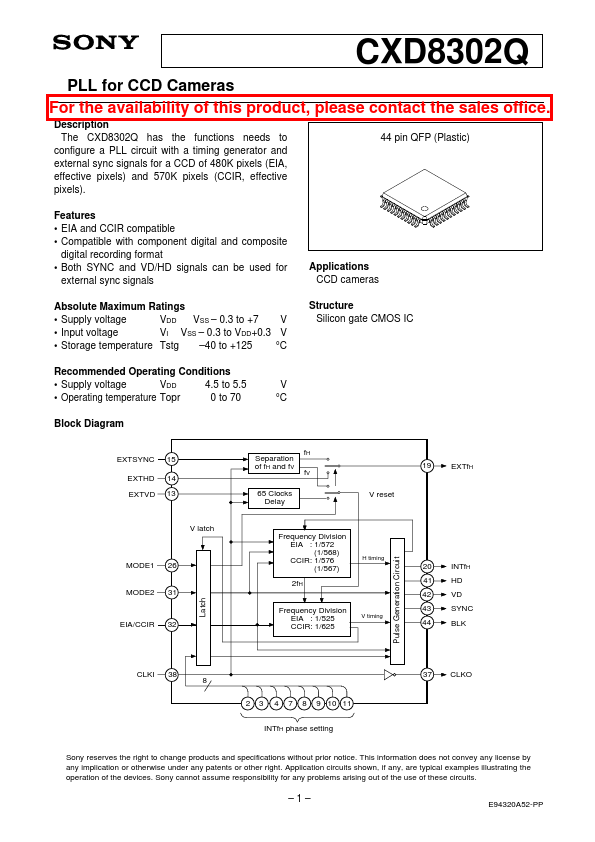

Description The CXD8302Q has the functions needs to configure a PLL circuit with a timing generator and external sync signals for a CCD of 480K pixels (EIA, effective pixels) and 570K pixels (CCIR, effective pixels). Features

- EIA and CCIR patible

- patible with ponent digital and posite digital recording format

- Both SYNC and VD/HD signals can be used for external sync signals...