W196

Features

- Maximized EMI suppression using Cypress’s Spread Spectrum Technology

..

- System frequency synthesizer for 440BX, 440ZX, and

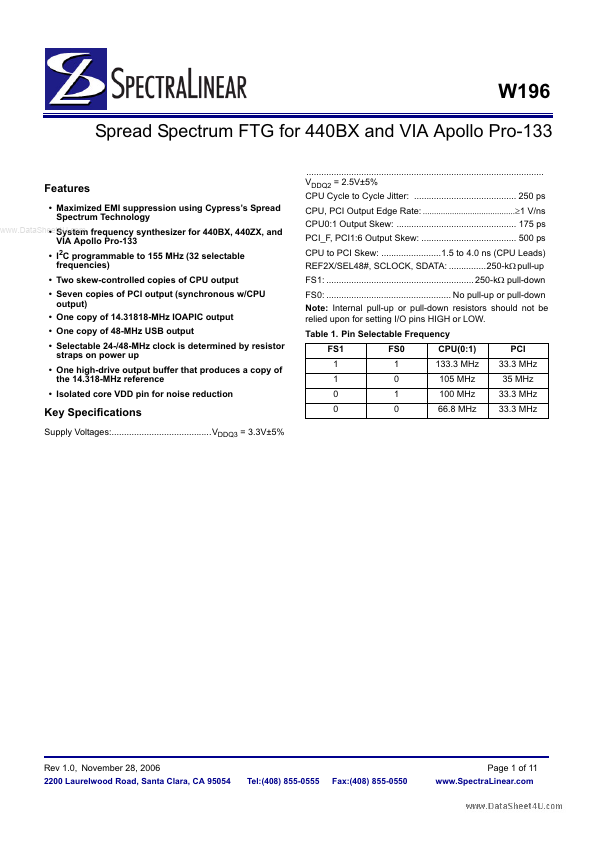

VDDQ2 = 2.5V±5% CPU Cycle to Cycle Jitter: 250 ps CPU, PCI Output Edge Rate: t1 V/ns CPU0:1 Output Skew: 175 ps PCI_F, PCI1:6 Output Skew: 500 ps CPU to PCI Skew: 1.5 to 4.0 ns (CPU Leads) REF2X/SEL48#, SCLOCK, SDATA: 250-k: pull-up FS1: 250-k: pull-down FS0: No pull-up or pull-down Note: Internal pull-up or pull-down resistors should not be relied upon for setting I/O pins HIGH or LOW. Table 1. Pin Selectable Frequency FS1 1 1 0 0 FS0 1 0 1...