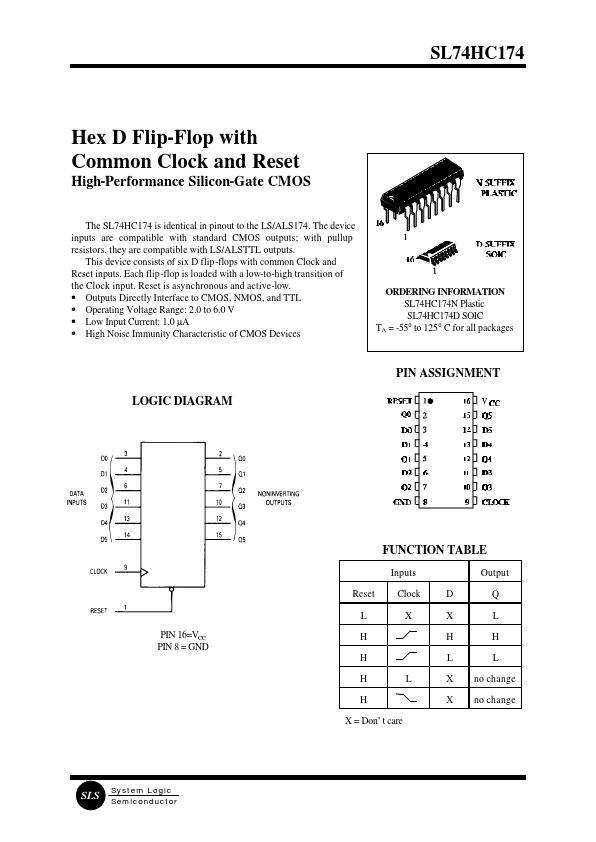

| Part | SL74HC174 |

|---|---|

| Description | Hex D Flip-Flop with Common Clock and Reset |

| Manufacturer | System Logic Semiconductor |

| Size | 46.08 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| NCP803 | onsemi | Very Low Supply Current 3-Pin Microprocessor Reset Monitor |

| CAT823 | onsemi | System Supervisory Voltage Reset |

| MAX809 | Maxim Integrated | 3-Pin Microprocessor Reset Circuits |