QLS1026A Datasheet Text

QLS1046A, QLS1026A

Qormino Integrated Multicore munication processor with 4GB of DDR4

Preliminary datasheet DS 60S 217489

Features

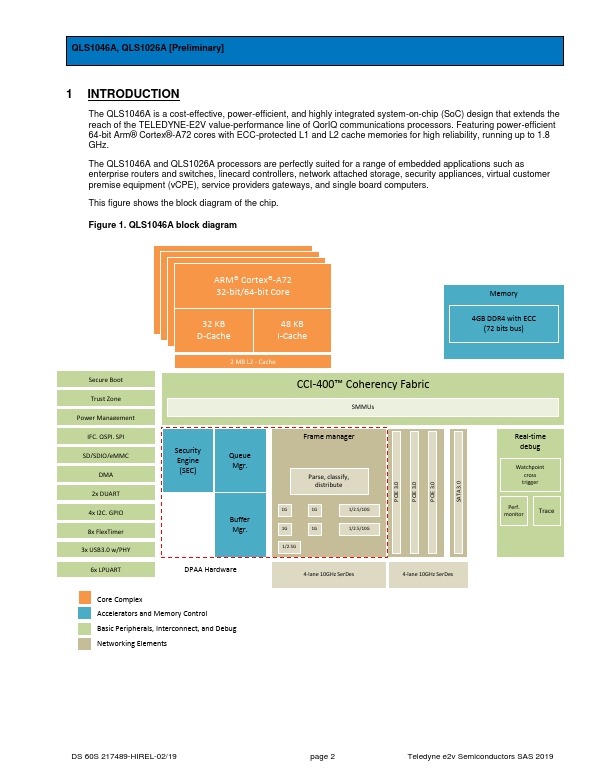

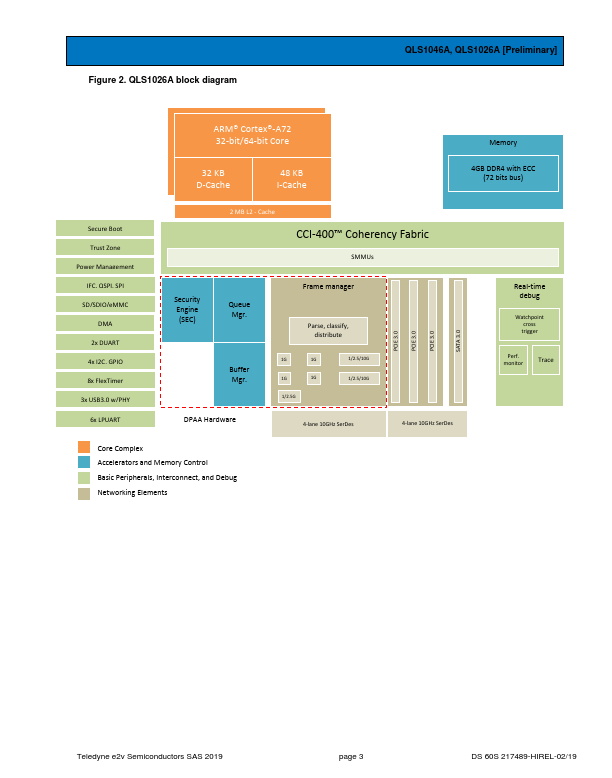

- QLS1046A has four cores and QLS1026A has two cores

- 4GB of DDR4 with ECC

- Four 32-bit/64-bit Arm® Cortex®-v8 A72 CPUs

- Arranged as a single cluster of four cores sharing a single 2 MB L2 cache

- Up to 1.8 GHz operation

- Single-threaded cores with 32 KB L1 data cache and 48 KB L1 instruction cache

- Hierarchical interconnect fabric

- Up to 700 MHz operation

- Data Path Acceleration Architecture (DPAA) incorporating acceleration for the following functions:

- Packet parsing, classification, and distribution (FMan)

- Queue management for scheduling, packet sequencing, and congestion management (QMan)

- Hardware buffer management for buffer allocation and de-allocation (BMan)

- Cryptography acceleration (SEC)

- IEEE 1588™ support

- Two RGMII interfaces

- Eight SerDes lanes for high-speed peripheral interfaces

- Three PCI Express 3.0 controllers

- One Serial ATA (SATA 6 Gbit/s) controller

- Up to two XFI (10 GbE) interfaces

- Up to five SGMII interfaces supporting 1000 Mbps

- Up to three SGMII interfaces supporting 2500 Mbps

- Up to one QSGMII interface

- Supports 10GBase-KR

- Supports 1000Base-KX

- Additional peripheral interfaces

- One Quad Serial Peripheral Interface (QSPI) controller...