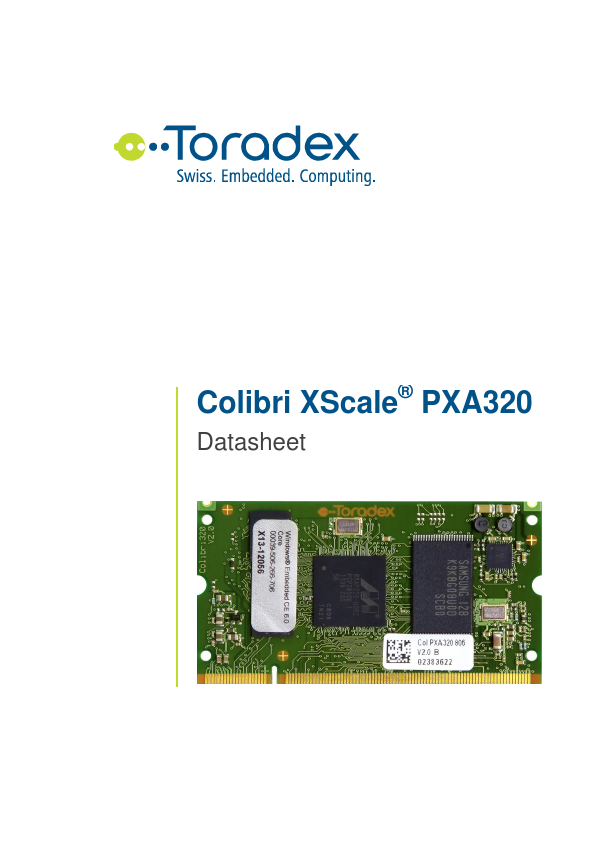

| Part | PXA320 |

|---|---|

| Description | Colibri Xscale |

| Manufacturer | Toradex |

| Size | 822.82 KB |

Pricing from 27 USD, available from ICPartonline and Antdic Electronics.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| ICPartonline | 37992 | 1+ : 27 USD 10+ : 25.65 USD 100+ : 24.3 USD 1000+ : 22.95 USD |

View Offer |

| Antdic Electronics | 31430 | 1+ : 20 USD 10+ : 19 USD 100+ : 18 USD 1000+ : 16 USD |

View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| PXA320 | Strategic | Module |