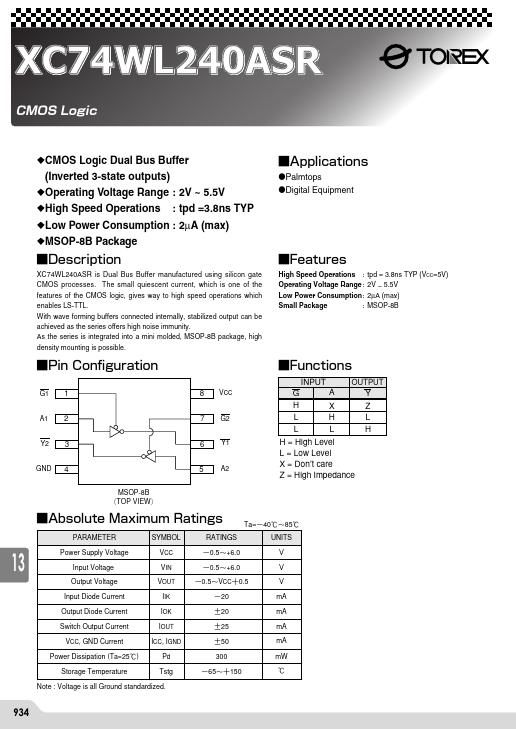

XC74WL240ASR

Key Features

- of the CMOS logic, gives way to high speed operations which enables LS-TTL

- With wave forming buffers connected internally, stabilized output can be achieved as the series offers high noise immunity

- As the series is integrated into a mini molded, MSOP-8B package, high density mounting is possible