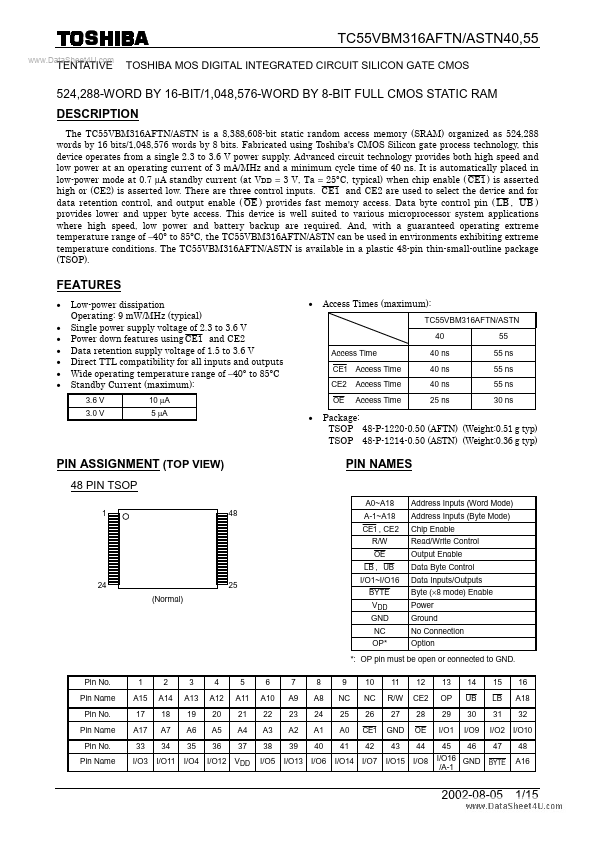

TC55VBM316AFTN Overview

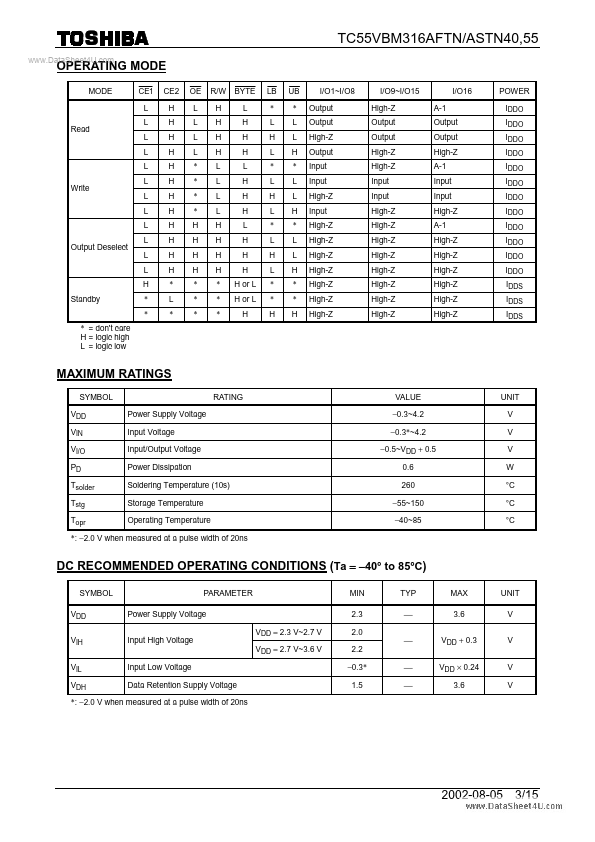

Fabricated using Toshiba's CMOS Silicon gate process technology, this device operates from a single 2.3 to 3.6 V power supply. Advanced circuit technology provides both high speed and low power at an operating current of 3 mA/MHz and a minimum cycle time of 40 ns. It is automatically placed in low-power mode at 0.7 µA standby current (at VDD = 3 V, Ta = 25°C, typical) when chip enable ( CE1 ) is asserted high or...

TC55VBM316AFTN Key Features

- Access Times (maximum)