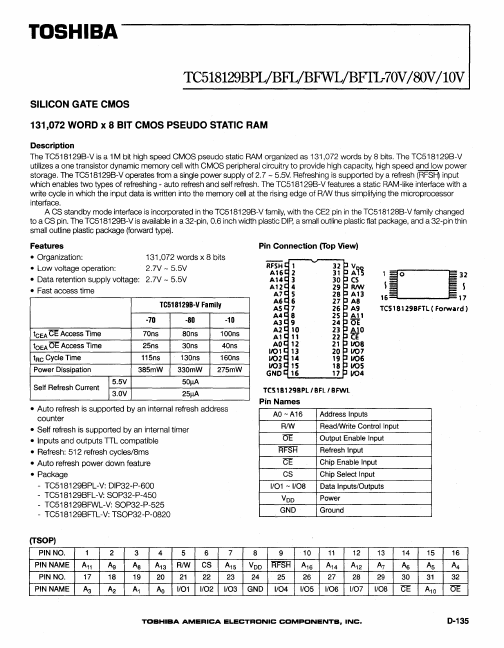

| Part | TC518129BFWL-10V |

|---|---|

| Description | SILICON GATE CMOS PSEUDO STATIC RAM |

| Manufacturer | Toshiba |

| Size | 473.01 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| HT16K33 | Holtek Semiconductor | RAM Mapping 16 x 8 LED Controller Driver |

| M58725P | Mitsubishi Electric | 16K-Bit Static RAM |

| HT1621B | HTCSEMI | RAM Mapping 32x4 LCD Controller |