TC551001API-85

Description

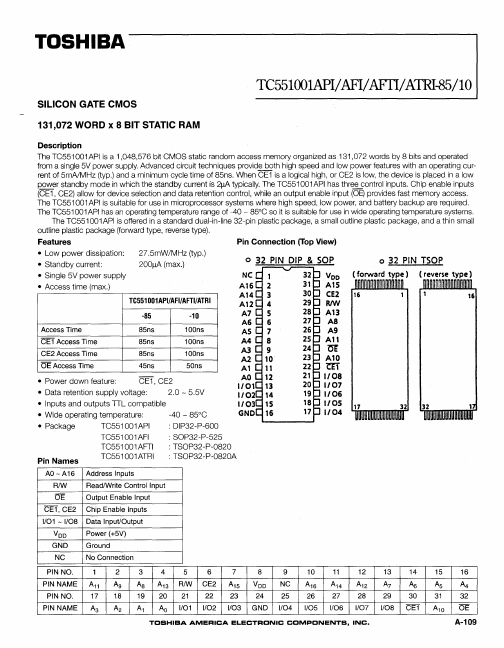

The TC551 001 API is a 1,048,576 bit CMOS static random access memory organized as 131,072 words by 8 bits and operated from a single 5V power supply. Advanced circuit techniques provide both high speed and low power features with an operating current of 5mNMHz (typ.) and a minimum cycle time of 85ns.