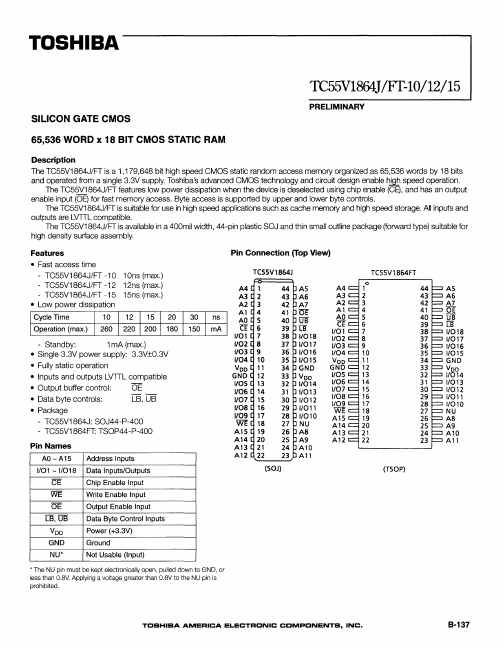

- Part: TC55V1864FT-10

- Description: 18-Bit CMOS SRAM

- Manufacturer: Toshiba

- Size: 251.64 KB

Related Toshiba Datasheets

| Part Number | Description |

|---|---|

| TC55V1864FT-12 | 18-Bit CMOS SRAM |

| TC55V1864FT-15 | 18-Bit CMOS SRAM |

| TC55V1864J-10 | 18-Bit CMOS SRAM |

| TC55V1864J-12 | 18-Bit CMOS SRAM |

| TC55V1864J-15 | 18-Bit CMOS SRAM |